完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > Cadence

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個(gè)專門從事電子設(shè)計(jì)自動(dòng)化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設(shè)計(jì)技術(shù)(Electronic Design Technologies)、程序方案服務(wù)和設(shè)計(jì)服務(wù)供應(yīng)商。其解決方案旨在提升和監(jiān)控半導(dǎo)體、計(jì)算機(jī)系統(tǒng)、網(wǎng)絡(luò)工程和電信設(shè)備、消費(fèi)電子產(chǎn)品以及其它各類型電子產(chǎn)品的設(shè)計(jì)。

同時(shí)宣布針對臺積公司 N3C 工藝的工具認(rèn)證完成,并基于臺積公司最新 A14 技術(shù)展開初步合作 中國上海,2025 年

2025-05-23 標(biāo)簽: 臺積電 Cadence 芯片設(shè)計(jì) 368 0

Cadence SPB OrCAD Allegro22.1安裝包

包括了Capture原理圖設(shè)計(jì)、PSpice仿真、Alelgro PCB Editor及PCB SI組件?系統(tǒng)需求Cad

Cadence SPB OrCAD Allegro23.1安裝包

OrCAD X 是一個(gè)創(chuàng)新的設(shè)計(jì)平臺,可滿足個(gè)人和中小型企業(yè)的需求。它專注于為所有設(shè)計(jì)需求提供具有凝聚力的綜合解決方案。

Cadence SPB OrCAD Allegro24.1安裝包

Cadence SPB(Silicon Package Board)是一套電子設(shè)計(jì)自動(dòng)化(EDA)軟件套件,主要用于集成

Cadence推出Tensilica NeuroEdge 130 AI協(xié)處理器

楷登電子(美國 Cadence 公司,Nasdaq:CDNS)近日宣布推出 Cadence Tensilica Neur

DesignCon 采訪 | Cadence 的前瞻性方法和先進(jìn)封裝設(shè)計(jì)的未來

隨著半導(dǎo)體產(chǎn)業(yè)快速發(fā)展,人工智能加速推動(dòng)對高性能計(jì)算的需求,Cadence將自己定位為仿真和設(shè)計(jì)自動(dòng)化領(lǐn...

2025-05-16 標(biāo)簽: Cadence 人工智能 封裝設(shè)計(jì) 208 0

Celestial AI 在 Virtuoso Studio 環(huán)境中采用Cadence方案進(jìn)行智能RC調(diào)試、優(yōu)化和簽核

? ? ? AI 模型規(guī)模的爆炸式增長促使業(yè)內(nèi)對低延遲內(nèi)存帶寬和容量的需求出現(xiàn)激增。Celestial AI 一直在與多

網(wǎng)課回放 I 升級版“一站式” PCB 設(shè)計(jì)第三期:原理圖完整性及可靠性分析

網(wǎng)課回放 I 升級版“一站式” PCB 設(shè)計(jì)第三期:原理圖完整性及可靠性分析

2025-05-10 標(biāo)簽: Cadence PCB 設(shè)計(jì) 110 0

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布率先推出基于臺積公司 N3 工藝的 DDR5 12

Condor使用Cadence托管云服務(wù)開發(fā)高性能RISC-V微處理器

Condor 是一家美國初創(chuàng)企業(yè),致力于開發(fā)高性能 RISC-V 微處理器。公司的目標(biāo)是通過創(chuàng)新技術(shù)徹底革新整個(gè)行業(yè...

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個(gè)專門從事電子設(shè)計(jì)自動(dòng)化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設(shè)計(jì)技術(shù)(Electronic Design Technologies)、程序方案服務(wù)和設(shè)計(jì)服務(wù)供應(yīng)商。其解決方案旨在提升和監(jiān)控半導(dǎo)體、計(jì)算機(jī)系統(tǒng)、網(wǎng)絡(luò)工程和電信設(shè)備、消費(fèi)電子產(chǎn)品以及其它各類型電子產(chǎn)品的設(shè)計(jì)。

電話: 86.21.61222300

傳真: 86.21.60312555

Cadence Allegro系統(tǒng)互連平臺能夠跨集成電路、封裝和PCB協(xié)同設(shè)計(jì)高性能互連。應(yīng)用平臺的協(xié)同設(shè)計(jì)方法,工程師可以迅速優(yōu)化I/O緩沖器之間和跨集成電路、封裝和PCB的系統(tǒng)互聯(lián)。該方法能避免硬件返工并降低硬件成本和縮短設(shè)計(jì)周期。約束驅(qū)動(dòng)的Allegro流程包括高級功能用于設(shè)計(jì)捕捉、信號完整性和物理實(shí)現(xiàn)。由于它還得到Cadence Encounter與Virtuoso平臺的支持,Allegro協(xié)同設(shè)計(jì)方法使得高效的設(shè)計(jì)鏈協(xié)同成為現(xiàn)實(shí)。

Broadcom使用Cadence Spectre FMC Analysis進(jìn)行時(shí)序變化分析

對于最新的微型半導(dǎo)體制作工藝而言,制程工藝變化和器件不匹配帶來了深遠(yuǎn)影響。復(fù)雜制程工藝也會影響器件生產(chǎn)的可變性,進(jìn)而影響整體良品率。 蒙特卡洛(MC...

Cadence解決方案助力高性能傳感器封裝設(shè)計(jì)

在技術(shù)和連通性主宰一切的時(shí)代,電子和機(jī)械設(shè)計(jì)的融合將徹底改變用戶體驗(yàn)。獨(dú)立開發(fā)器件的時(shí)代已經(jīng)過去;市場對創...

Allegro Skill封裝功能-導(dǎo)出device文件介紹與演示

Device文件定義了原理圖中的符號(Symbol)與實(shí)際PCB布局中的封裝(Footprint)之間的對應(yīng)關(guān)系。例如,一個(gè)電阻的原理圖符號可能對應(yīng...

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實(shí)現(xiàn)流片成功

我們很高興能在此宣布,Cadence 基于 UCIe 標(biāo)準(zhǔn)封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實(shí)現(xiàn)首次流片成功。這一....

如何使用Python API創(chuàng)建自定義函數(shù)

Cadence 統(tǒng)一調(diào)試平臺 Verisium Debug 提供多種調(diào)試功能,如 RTL 調(diào)試、UVM 仿真平臺調(diào)試、UPF 調(diào)...

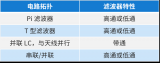

Cadence技術(shù)解讀 天線的阻抗匹配技術(shù)

本文要點(diǎn) 天線的阻抗匹配技術(shù)旨在確保將最大功率傳輸?shù)教炀€中,從而使天線元件能夠強(qiáng)烈輻射。 天線阻抗匹配是指將天線饋線末端的輸入阻抗與饋線的特性阻抗相匹配....

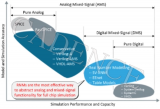

利用實(shí)數(shù)建模簡化混合信號驗(yàn)證流程

混合信號設(shè)計(jì)在半導(dǎo)體設(shè)計(jì)飛速發(fā)展的過程中發(fā)揮著關(guān)鍵作用。混合信號設(shè)計(jì)將模擬與數(shù)字電路無縫集成至一個...

1.開機(jī)和開軟件 開機(jī)啟動(dòng)后是這個(gè)畫面 賬號: 密碼: 右鍵屏幕左擊open terminal 命令行里面打入如下圖的命令 ls 和 cd 是linux...

2024-11-16 標(biāo)簽:電路設(shè)計(jì)Cadence 3297 0

如何在Cadence的EMX仿真中精準(zhǔn)設(shè)置長邊PORT

請問在Cadence的EMX仿真里,如果需要在一個(gè)較長的邊打PORT,需要怎么設(shè)置會仿真比較精準(zhǔn)?像這樣子直接吸附一個(gè)上去可以嗎?

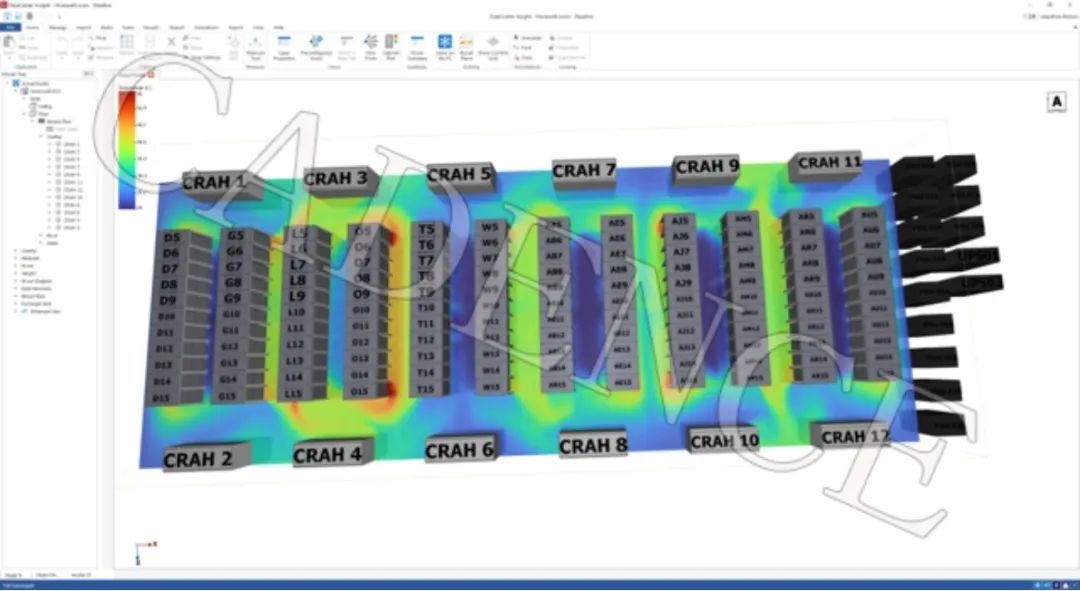

霍尼韋爾IQVISION和Cadence數(shù)據(jù)中心數(shù)字孿生的全新集成

垃圾進(jìn),垃圾出。數(shù)字孿生模型的好壞取決于輸入數(shù)據(jù)的質(zhì)量。

2024-08-29 標(biāo)簽:霍尼韋爾Cadence數(shù)據(jù)中心 786 0

0

0

最近配置Cadence的共享cis庫,按照相關(guān)步驟配置完成之后,調(diào)用元器件會出現(xiàn)原理圖錯(cuò)誤,求大佬指教

標(biāo)簽:Cadence 9734 0

2024-03-07 標(biāo)簽:Cadence 0 1421

同時(shí)宣布針對臺積公司 N3C 工藝的工具認(rèn)證完成,并基于臺積公司最新 A14 技術(shù)展開初步合作 中國上海,2025 年 5 月 23 日——楷登電子(美...

2025-05-23 標(biāo)簽:臺積電Cadence芯片設(shè)計(jì) 368 0

Cadence推出Tensilica NeuroEdge 130 AI協(xié)處理器

楷登電子(美國 Cadence 公司,Nasdaq:CDNS)近日宣布推出 Cadence Tensilica NeuroEdge 130 AI 協(xié)處理...

DesignCon 采訪 | Cadence 的前瞻性方法和先進(jìn)封裝設(shè)計(jì)的未來

隨著半導(dǎo)體產(chǎn)業(yè)快速發(fā)展,人工智能加速推動(dòng)對高性能計(jì)算的需求,Cadence將自己定位為仿真和設(shè)計(jì)自動(dòng)化領(lǐn...

2025-05-16 標(biāo)簽:Cadence人工智能封裝設(shè)計(jì) 208 0

Celestial AI 在 Virtuoso Studio 環(huán)境中采用Cadence方案進(jìn)行智能RC調(diào)試、優(yōu)化和簽核

? ? ? AI 模型規(guī)模的爆炸式增長促使業(yè)內(nèi)對低延遲內(nèi)存帶寬和容量的需求出現(xiàn)激增。Celestial AI 一直在與多家大型服務(wù)商合作,以深...

網(wǎng)課回放 I 升級版“一站式” PCB 設(shè)計(jì)第三期:原理圖完整性及可靠性分析

網(wǎng)課回放 I 升級版“一站式” PCB 設(shè)計(jì)第三期:原理圖完整性及可靠性分析

2025-05-10 標(biāo)簽:CadencePCB 設(shè)計(jì) 110 0

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布率先推出基于臺積公司 N3 工藝的 DDR5 12.8Gbps MRDIMM Ge...

Condor使用Cadence托管云服務(wù)開發(fā)高性能RISC-V微處理器

Condor 是一家美國初創(chuàng)企業(yè),致力于開發(fā)高性能 RISC-V 微處理器。公司的目標(biāo)是通過創(chuàng)新技術(shù)徹底革新整個(gè)行業(yè...

Cadence收購Arm基礎(chǔ)IP業(yè)務(wù),誰是贏家?

電子發(fā)燒友網(wǎng)報(bào)道(文/梁浩斌)最近EDA公司密集收購半導(dǎo)體IP公司,就在上周國內(nèi)EDA廠商概倫電子宣布收購銳成芯微100%股權(quán)和納能微45...

瑞芯微RK2118 SoC搭載Cadence Tensilica HiFi 4 DSP

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)與瑞芯微電子股份有限公司(以下簡稱“瑞芯微”,股票代碼:603893)今日共同宣布在音頻處...

為了提供更好的用戶體驗(yàn),包括高質(zhì)量的視頻傳輸、更新的筆記本電腦(例如最新的 AI PC)和其他前沿設(shè)備,都需要 5 納米及以下的先進(jìn)節(jié)點(diǎn) ...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題 教程专题

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |