京微齊力HME-P2系列FPGA的pSRAM讀寫例程分析

最近有客戶反映國(guó)產(chǎn)FPGA京微齊力P2器件內(nèi)部合封的pSRAM控制器讀寫效率很高,能達(dá)80%以上,而且合封了4片8bit位寬pSRAM芯片,按250MHz主頻DDR雙沿讀寫算下來80%效率能跑出12.8Gbps的極限帶寬,即使考慮工程布局布線的限制影響因素,按210MHz主頻也應(yīng)能跑出10.5Gbps讀寫帶寬。

- 專欄HME京微齊力

- 1天前

- 451

- 0

- 0

FPGA 大神 Adam Taylor 使用 ALINX VD100(AMD Versal系列)開發(fā)平臺(tái)實(shí)現(xiàn)圖像處理

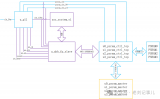

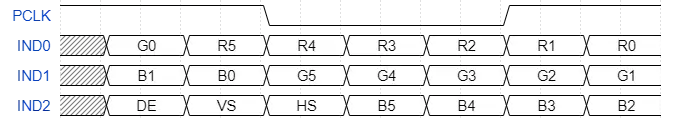

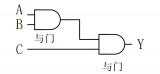

本篇文章來自 FPGA 大神、Ardiuvo XVtc VtcInst;VideoMode video;XVtc_Config *vtc_config ;int main(){ XVtc_SourceSelect SourceSelect; XVtc_Timing vtcTiming; u32 height,width,status; init_platform(); print("Setting up Timingnr"); vtc_config = XVtc_LookupConfig(XPAR_XVTC_0_BASEADDR); XVtc_CfgInitialize( print("Setting up Videonr"); video = VMODE_1280x720 ;vtcTiming.HActiveVideo = video.width;vtcTiming.HFrontPorch = video.hps - video.width;vtcTiming.HSyncWidth = video.hpe - video.hps;vtcTiming.HBackPorch = video.hmax - video.hpe + 1;vtcTiming.HSyncPolarity = video.hpol;vtcTiming.VActiveVideo

- 專欄FPGA技術(shù)專欄

- 1天前

- 327

- 0

- 0

FPGA的定義和基本結(jié)構(gòu)

FPGA 的全稱為 Field-Programmable Gate Array,即現(xiàn)場(chǎng)可編程門陣列。 FPGA 是在 PAL、 GAL、 CPLD 等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物, 是作為專用集成電路( ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。 簡(jiǎn)而言之, FPGA 就是一個(gè)可以通過編程來改變內(nèi)部結(jié)構(gòu)的芯片。

- 專欄FPGA設(shè)計(jì)論壇

- 2天前

- 349

- 0

- 0

2025紫光同創(chuàng)FPGA技術(shù)研討會(huì)深圳/廣州站:小眼睛科技國(guó)產(chǎn)FPGA方案助您開啟智能新紀(jì)元

“2025紫光同創(chuàng)FPGA技術(shù)研討會(huì)”深圳站&廣州站即將盛大啟航!作為紫光同創(chuàng)生態(tài)合作伙伴,小眼睛科技將攜多個(gè)基于紫光同創(chuàng)FPGA方案亮相,此次展示的解決方案覆蓋了工業(yè)自動(dòng)化、音視頻處理、網(wǎng)絡(luò)通信等多個(gè)關(guān)鍵領(lǐng)域。我們將以卓越的技術(shù)實(shí)力和豐富的行業(yè)經(jīng)驗(yàn),助力各領(lǐng)域?qū)崿F(xiàn)智能化升級(jí),共同開啟智能科技的新篇章。方案1:基于紫光同創(chuàng)Logos2的多屏分割器基于紫光同創(chuàng)

- 企業(yè)小眼睛科技

- 4天前

- 267

- 0

- 0

紫光同創(chuàng)Logos2+RK3568開發(fā)板:國(guó)產(chǎn)器件強(qiáng)強(qiáng)聯(lián)合開啟嵌入式開發(fā)新篇章

國(guó)產(chǎn)芯片的崛起與創(chuàng)新組合RK3568:強(qiáng)大性能的核心引擎紫光同創(chuàng)PG2L50H靈活定制的硬件利器強(qiáng)強(qiáng)聯(lián)合聚勢(shì)而生RK3568+紫光同創(chuàng)PG2L50HRK3568與紫光同創(chuàng)PG2L50H相結(jié)合,二者的優(yōu)勢(shì)得到充分的互補(bǔ)與放大。一方面,RK3568強(qiáng)大的通用計(jì)算能力和豐富的軟件生態(tài),能夠運(yùn)行復(fù)雜的操作系統(tǒng)和應(yīng)用程序,實(shí)現(xiàn)系統(tǒng)的整體管理與控制。另一方面,紫光同創(chuàng)L

- 企業(yè)小眼睛科技

- 4天前

- 349

- 0

- 0

FPGA芯片的概念和結(jié)構(gòu)

FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列),是一種可在出廠后由用戶根據(jù)實(shí)際需求進(jìn)行編程配置的集成電路。與專用集成電路(如ASIC)不同,F(xiàn)PGA在硬件層面具備高度的可重構(gòu)性,能夠靈活實(shí)現(xiàn)各類數(shù)字邏輯電路和復(fù)雜系統(tǒng)方案。

- 專欄中科院半導(dǎo)體所

- 5天前

- 323

- 0

- 0

原軟件定義汽車時(shí)代,Elektrobit談虛擬開發(fā)到量產(chǎn)落地的效率躍升

電子發(fā)燒友網(wǎng)報(bào)道(文 / 吳子鵬)軟件定義汽車(Software-Defined Vehicle, SDV)正掀起汽車產(chǎn)業(yè)的革命性變革,推動(dòng)行業(yè)從機(jī)械硬件主導(dǎo)邁向軟件技術(shù)驅(qū)動(dòng)的新階段。其核心在于實(shí)現(xiàn)硬件與軟件的解耦,借助軟件實(shí)現(xiàn)車輛功能的動(dòng)態(tài)定義與持續(xù)迭代,為汽車行業(yè)帶來全新的發(fā)展機(jī)遇。? ? SDV 從架構(gòu)、軟件和通信等層面深刻重塑當(dāng)前汽車設(shè)計(jì)格局。在架構(gòu)方面,域控制器整合功能,逐步取代傳統(tǒng)分布式 ECU 架構(gòu),有效減少硬件冗余;未來,車載架構(gòu)將進(jìn)一步向

- 842221752

- 5天前

- 4861

- 0

- 0

中科億海微亮相2025中國(guó)圖象圖形大會(huì),共繪圖像圖形“芯”未來!

2025年5月8日至11日,中國(guó)圖像圖形領(lǐng)域頂級(jí)學(xué)術(shù)盛會(huì)——中國(guó)圖象圖形大會(huì)(CCIG2025)在湖南長(zhǎng)沙圓滿落幕!作為圖像圖形領(lǐng)域的年度盛會(huì),本次大會(huì)匯聚了國(guó)內(nèi)外頂尖學(xué)者、行業(yè)領(lǐng)袖及創(chuàng)新企業(yè),共同探討前沿技術(shù)趨勢(shì)與產(chǎn)業(yè)應(yīng)用。中科億海微以創(chuàng)新者姿態(tài),攜自主研發(fā)的高可靠FPGA芯片及一系列專業(yè)解決方案亮相。憑借卓越的技術(shù)性能與廣泛的應(yīng)用前景,中科億海微的展品迅

- 企業(yè)中科億海微

- 6天前

- 222

- 0

- 0

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應(yīng)SoC設(shè)計(jì)

設(shè)計(jì)、編譯、交付,輕松搞定。更快更高效。 Vivado 設(shè)計(jì)套件提供經(jīng)過優(yōu)化的設(shè)計(jì)流程,讓傳統(tǒng) FPGA 開發(fā)人員能夠加快完成 Versal 自適應(yīng) SoC 設(shè)計(jì)。 面向硬件開發(fā)人員的精簡(jiǎn)設(shè)計(jì)流程 ? - 頂層 RTL 流程 - 通過使用頂層 RTL,用戶能夠像配置片上網(wǎng)絡(luò)和收發(fā)器一樣配置關(guān)鍵的硬核 IP,從而獲得類似于傳統(tǒng) FPGA 設(shè)計(jì)的體驗(yàn)。 - 快速編譯 - 全新“高級(jí)流程”實(shí)現(xiàn)算法融合了分層設(shè)計(jì)優(yōu)化和并行執(zhí)行機(jī)制,可有效解決擁塞、可布線性和運(yùn)行時(shí)等問題。 - 優(yōu)先啟動(dòng)處理

- 專欄Xilinx賽靈思官微

- 10天前

- 269

- 0

- 0

FPGA芯片選型的核心原則

本文總結(jié)了FPGA選型的核心原則和流程,旨在為設(shè)計(jì)人員提供決策依據(jù),確保項(xiàng)目成功。

- 專欄中科院半導(dǎo)體所

- 17天前

- 302

- 0

- 0

國(guó)產(chǎn)FPGA公司高云半導(dǎo)體榮獲 “年度汽車產(chǎn)業(yè)鏈突破獎(jiǎng)”,引領(lǐng)車規(guī)芯片發(fā)展

4月25日-26日,由《中國(guó)汽車報(bào)》有限公司、上海車展管理有限公司、汽車電子產(chǎn)業(yè)投資聯(lián)盟聯(lián)合主辦,愛集微咨詢(廈門)有限公司協(xié)辦的“2025汽車半導(dǎo)體生態(tài)大會(huì)暨中國(guó)車規(guī)芯片技術(shù)路演”在國(guó)家會(huì)展中心(上海)圓滿舉行。廣東高云半導(dǎo)體科技股份有限公司(簡(jiǎn)稱“高云半導(dǎo)體”)受邀出席本次大會(huì),并憑借在汽車電子領(lǐng)域的卓越表現(xiàn),榮獲了由汽車電子產(chǎn)業(yè)投資聯(lián)盟、《中國(guó)汽車報(bào)》和愛集微聯(lián)合評(píng)定的"年度汽車產(chǎn)業(yè)鏈突破獎(jiǎng)(2024-2025)"。 "年

- 專欄高云半導(dǎo)體

- 20天前

- 422

- 0

- 0

FPGA的Jtag接口燒了,怎么辦?

在展開今天的文章前,先來討論一個(gè)問題:FPGA的jtag接口燒了怎么辦?JTAG接口的輸入引腳通常設(shè)計(jì)為高阻抗,這使得它們對(duì)靜電電荷積累非常敏感,由于JTAG接口需要頻繁連接調(diào)試器、下載線纜等外部設(shè)備,插拔過程中極易因摩擦產(chǎn)生靜電。JTAG接口經(jīng)常會(huì)有帶電拔插的情況,這不可避免地會(huì)產(chǎn)生靜電或浪涌電流。JTAG接口的引腳直接與FPGA內(nèi)部的測(cè)試訪問端口(TAP

- 企業(yè)小眼睛科技

- 20天前

- 312

- 0

- 0

原Cadence收購(gòu)Arm基礎(chǔ)IP業(yè)務(wù),誰是贏家?

電子發(fā)燒友網(wǎng)報(bào)道(文/梁浩斌)最近EDA公司密集收購(gòu)半導(dǎo)體IP公司,就在上周國(guó)內(nèi)EDA廠商概倫電子宣布收購(gòu)銳成芯微100%股權(quán)和納能微45.64%股權(quán)之后,4月16日,國(guó)際EDA巨頭Cadence在官網(wǎng)上發(fā)文宣布與Arm達(dá)成最終協(xié)議,收購(gòu)Arm的Artisan foundation IP業(yè)務(wù),包括標(biāo)準(zhǔn)單元庫(kù)、嵌入式內(nèi)存和GPIOs等產(chǎn)品。 ? 一直以來,EDA企業(yè)都通過積極的并購(gòu)和與半導(dǎo)體IP協(xié)同的模式進(jìn)行擴(kuò)張,并購(gòu)IP公司是EDA整合產(chǎn)業(yè)鏈、提升技術(shù)壁壘、應(yīng)對(duì)市場(chǎng)挑戰(zhàn)的關(guān)鍵策略。 ? Artisan 業(yè)務(wù)狀況

- 專欄Hobby觀察

- 21天前

- 2405

- 0

- 0

喜訊!米爾電子與安路科技達(dá)成IDH生態(tài)戰(zhàn)略合作,共筑FPGA創(chuàng)新生態(tài)

以芯為基,智創(chuàng)未來。近日,領(lǐng)先的嵌入式模組廠商-米爾電子正式與國(guó)產(chǎn)FPGA企業(yè)?安路科技達(dá)成IDH生態(tài)戰(zhàn)略合作?。雙方將圍繞安路科技飛龍SALDRAGON系列高性能FPSoC,聯(lián)合開發(fā)核心板、開發(fā)板及行業(yè)解決方案,助力開發(fā)者開發(fā)成功,加速工業(yè)控制、邊緣智能、汽車電子等領(lǐng)域的創(chuàng)新應(yīng)用落地?。米爾電子&安路科技IDH生態(tài)合作證書?硬核技術(shù)+生態(tài)協(xié)同?安路科技作為

- 企業(yè)米爾電子

- 22天前

- 947

- 0

- 0

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

Ultrascale是賽靈思開發(fā)的支持包含步進(jìn)功能的增強(qiáng)型FPGA架構(gòu),相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個(gè)系列:Kintex和Virtex。Ultrascale+采用16ns,有3個(gè)系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進(jìn),如時(shí)鐘資源與架構(gòu),本文將重點(diǎn)介紹Ultrascale的時(shí)鐘資源與架構(gòu),Ultrascale+和Ultrascale大體上相似。

- 專欄FPGA設(shè)計(jì)論壇

- 23天前

- 566

- 0

- 0

京微齊力亮相2025慕尼黑上海電子展

此前,4月15日-17日,為期三天的2025慕尼黑上海電子展(Electronica China 2025)在上海新國(guó)際博覽中心成功舉辦。京微齊力攜多項(xiàng)產(chǎn)品及豐富的解決方案重磅亮相此次行業(yè)盛會(huì),集中展示了企業(yè)的技術(shù)研發(fā)成果。期間,憑借多項(xiàng)實(shí)體化應(yīng)用解決方案的展示,吸引了眾多與會(huì)者關(guān)注,通過與行業(yè)同仁的深入交流,進(jìn)一步了解用戶對(duì)于產(chǎn)品的實(shí)際落地需求,精準(zhǔn)把握市場(chǎng)風(fēng)向。

- 專欄HME京微齊力

- 26天前

- 516

- 0

- 0

Altera大學(xué)成立,助力FPGA教學(xué)發(fā)展與人才培養(yǎng)

近日,全球 FPGA 創(chuàng)新技術(shù)領(lǐng)導(dǎo)者 Altera 宣布成立 Altera 大學(xué),旨在以高效、便捷的方式助力 FPGA 教學(xué)發(fā)展與人才培養(yǎng)。Altera 大學(xué)為高校教授、科研人員和廣大學(xué)子提供精心設(shè)計(jì)的課程、豐富的軟件工具和可編程硬件,助力其深入探索 FPGA 技術(shù)。

- 專欄英特爾FPGA

- 28天前

- 408

- 0

- 0

英特爾向銀湖資本出售Altera 51%股份

英特爾公司宣布已達(dá)成最終協(xié)議,將旗下 Altera 業(yè)務(wù) 51% 的股份出售給全球技術(shù)投資巨頭銀湖資本(Silver Lake)。

- 專欄英特爾FPGA

- 28天前

- 471

- 0

- 0

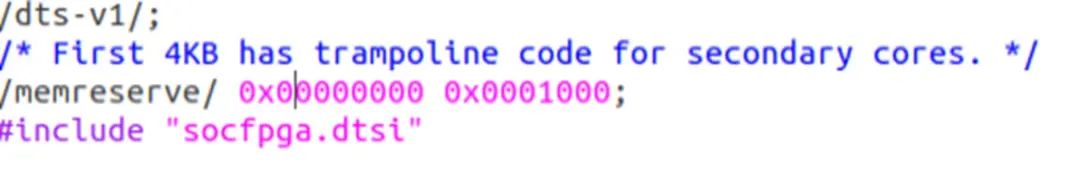

Linux系統(tǒng)中通過預(yù)留物理內(nèi)存實(shí)現(xiàn)ARM與FPGA高效通信的方法

在嵌入式系統(tǒng)開發(fā)中,ARM 和 FPGA 之間的通信可以使用 ARM 側(cè)的 DDR 作為通道。由于 FPGA 也可以直接訪問到 ARM 側(cè) DDR,但 DDR 作為共享通信時(shí),就不能被操作系統(tǒng)的內(nèi)存管理子系統(tǒng)管理。因此,需要預(yù)留一部分物理內(nèi)存,使其不被內(nèi)核管理。接下來將為大家詳細(xì)介紹在 Linux 系統(tǒng)中通過預(yù)留物理內(nèi)存實(shí)現(xiàn) ARM 與 FPGA 高效通信的方法,預(yù)留物理內(nèi)存包括 memreserve、Linux 內(nèi)核啟動(dòng)參數(shù) cmdline 和 Linux Reserved-Memory 三種方案。

- 專欄駿龍電子

- 1月前

- 471

- 0

- 0

易靈思2025 FPGA技術(shù)研討會(huì)北京站圓滿結(jié)束

易靈思2025FPGA技術(shù)研討會(huì)北京站于4月10日在北京麗亭華苑酒店圓滿結(jié)束!本次研討會(huì)吸引了來自全國(guó)各地的行業(yè)專家、工程師及企業(yè)代表踴躍參與,現(xiàn)場(chǎng)座無虛席,氣氛熱烈。

- 專欄易靈思官微

- 1月前

- 383

- 0

- 0