Celestial AI 在 Virtuoso Studio 環境中采用Cadence方案進行智能RC調試、優化和簽核

? ? ? AI 模型規模的爆炸式增長促使業內對低延遲內存帶寬和容量的需求出現激增。Celestial AI 一直在與多家大型服務商合作,以深入探究運算、內存和網絡系統基礎架構的瓶頸。Photonic Fabric?是業界唯一一款有能力打破“Memory Wall”并將數據直接傳輸到計算點的解決方案,同時能以極低的個位數 pJ/bit 功耗滿足當前的 HBM3E 和新一代 HBM4 帶寬和延遲要求。 ? Cadence Quantus Insight Solution? 改變了我們的設計流程,讓我們能夠快速識別并解決寄生參數相關的設計

- 專欄Cadence楷登

- 3天前

- 322

- 0

- 0

硬件輔助驗證(HAV) 對軟件驗證的價值

硬件輔助驗證 (HAV) 有著悠久的歷史,如今作為軟件驅動驗證的必備技術,再度受到關注。 RISC-V 可能是說明這一點的最好例子。HAV 能夠執行多個周期的軟件驅動驗證,是加速 RISC-V 生態系統和定制指令集開發的唯一途徑。 當下,芯片企業正在設計 RISC-V 人工智能 (AI) 與機器學習 (ML) 定制加速器,以實現特定工作負載的加速處理,這些企業創建的架構由軟件驅動,而不使用遺留數據或任何通用數據。而是,針對軟件工作負載應用在架構層面進行量身定制。

- 專欄西門子EDA

- 5天前

- 336

- 0

- 0

龍芯終端與合見工軟PCB設計軟件UniVista Archer成功適配

近日,龍芯3A5000/3A6000桌面終端與上海合見工業軟件集團有限公司自主研發的PCB設計軟件UniVista Archer成功適配,實現了電子系統設計平臺從電子硬件設計工具到硬件研發平臺的全國產化鏈路閉環。這一突破標志著龍芯終端在電子設計領域邁出關鍵一步,為“中國芯”的自主設計提供堅實底座。

- 專欄龍芯中科

- 5天前

- 238

- 0

- 0

概倫電子攜應用驅動的一站式芯片可靠性解決方案亮相ISEDA 2025,賦能設計公司COT平臺

5月10日,概倫電子副總裁劉文超博士受邀出席設計自動化領域國際盛會2025 International Symposium of EDA(ISEDA 2025),并發表《應用驅動的一站式芯片可靠性解決方案》主題演講,向行業同仁展示概倫電子在芯片可靠性設計領域的創新成果。該方案聚焦汽車電子領域,旨在通過前沿EDA技術助力行業應對高可靠性芯片設計挑戰,實現設計和驗證方法學突破。 隨著半導體技術的快速發展,制程工藝不斷向先進節點推進,工藝偏差、版圖效應、噪聲干擾、電壓降及電

- 專欄概倫電子Primarius

- 5天前

- 245

- 0

- 0

原第十五屆松山湖中國IC創新高峰論壇 “具身智慧”國產芯片集體亮相

由中國半導體行業協會集成電路設計分會、芯原微電子共同主辦的第十五屆松山湖中國IC創新高峰論壇今天在東莞松山凱悅酒店舉行,今年的主題是面向“具身智能機器人”的創新IC新品推介。中國半導體行業協會IC設計分會 副理事長,芯原股份創始人、董事長兼總裁戴偉民率先發言,對活動取得的成就做介紹,也對去年推介的產品做了回顧。電子發燒友網受邀在現場和后方作及時的報道。 ? 圖1:芯原股份戴偉民董事長在第十五屆松山湖中國IC創新高峰

- 專欄電子麥克風

- 5天前

- 4613

- 0

- 0

原華秋KiCad發行版 9.0.2發布:AI Copilot助力設計效率提升

“ ?本次新增加了 AI Copilot 助手,可以在原理圖、PCB 中讓智能助手與圖紙交互,幫助工程師更高效地理解圖紙、進行設計審查或者生成您想要的工程內容(如頭文件、設計方案等)? ” ? 華秋發行版概覽 華秋發行版是 開源 的 、非商業化的, 完全遵循 GPL 3.0 協議,且 跟隨 KiCad 最新的分支同步更新 。原則是 通用功能優先貢獻給 KiCad 主干 ,主干無法合并的功能才添加到發行版中,一旦主干可以支持,即刻合并到主干 。 因此發行版完全兼容 KiCad 的所有

- 專欄KiCad

- 8天前

- 2363

- 0

- 0

原KiCad 9.0.2 正式發布!

“ ? KiCad 9.0.2 正式發布! ” KiCad 9.0.2 版正式發布。9.0.2 穩定版本包含自上一版本以來的關鍵錯誤修復和其他小改進。 自 9.0.0 版本以來所有已修復問題的列表可以在 KiCad 9.0.2 里程碑頁面上找到: https://gitlab.com/groups/kicad/-/milestones/46 此版本包含多個關鍵錯誤修復,因此請考慮盡快升級。 9.0.2 版本是由 9.0 分支制作而成,并從開發分支中進行了一些精心挑選的更改。 適用于 Windows、macOS 和 Linux 的軟件包現已推出或將在不久的將來推出。請參閱 KiCad 下載頁

- 專欄KiCad

- 9天前

- 220

- 0

- 0

GUI Guider1.9.1新版本8大新亮點總結 為HMI開發注入新活力

GUI Guider迎來了全新版本!這一次,我們帶來了多項重磅更新,旨在為大家提供更強大、更便捷的開發體驗。無論你是工業控制、智能家居,還是消費電子領域的開發者,這些更新都將為你的項目注入新的活力! GUI Guider v1.9.1 ? 主要更新亮點 01 工程名稱支持更多字符 GUI Guider工程命名新增中劃線(-)和艾特(@)符號的支持,目前可用字符包括:字母、數字、下劃線(_)、中劃線(-)和艾特(@)。 02 支持自定義代碼生成路徑 支持生成目錄 (generated) 路徑

- 專欄NXP客棧

- 9天前

- 428

- 0

- 0

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

設計、編譯、交付,輕松搞定。更快更高效。 Vivado 設計套件提供經過優化的設計流程,讓傳統 FPGA 開發人員能夠加快完成 Versal 自適應 SoC 設計。 面向硬件開發人員的精簡設計流程 ? - 頂層 RTL 流程 - 通過使用頂層 RTL,用戶能夠像配置片上網絡和收發器一樣配置關鍵的硬核 IP,從而獲得類似于傳統 FPGA 設計的體驗。 - 快速編譯 - 全新“高級流程”實現算法融合了分層設計優化和并行執行機制,可有效解決擁塞、可布線性和運行時等問題。 - 優先啟動處理

- 專欄Xilinx賽靈思官微

- 11天前

- 282

- 0

- 0

EDA企業行芯科技入選國家先進制造業集群典型創新成果推介案例

近日,工業和信息化部工業文化發展中心正式發布國家先進制造業集群典型創新成果推介案例,杭州行芯科技有限公司“EDA簽核工具” 憑借在EDA(電子設計自動化)簽核領域的技術突破成功上榜,成為全國50個典型創新成果之一 。 此次評選聚焦先進制造業集群的創新引領性與產業貢獻度,旨在推廣具有示范效應的技術成果與產業實踐。行芯科技自2018年成立以來,持續致力于EDA簽核(Signoff)工具鏈領域的技術攻堅和創新,打造了包括寄生參數提取、電源

- 專欄行芯PHLEXING

- 12天前

- 572

- 0

- 0

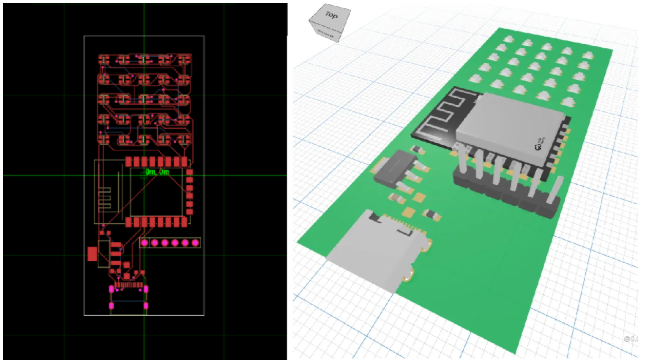

原tscircuit - 電路開發的 React 范式? 用TypeScript、React和 AI工具構建電子產品

用 TypeScript、React 和 AI 工具構建電子產品。

- 專欄KiCad

- 18天前

- 445

- 0

- 0

EDA工具鏈提供商行芯科技再登杭州準獨角獸企業榜單

2025年4月24日,民建浙江省委會、浙江省工商聯、中國投資發展促進會主辦的第九屆萬物生長大會在杭州舉辦。會上,備受矚目的《2025杭州獨角獸與準獨角獸企業榜單》正式發布。 杭州行芯科技有限公司作為國內領先的 EDA 工具鏈提供商再度榮耀登榜,這也是行芯科技連續第三年獲此殊榮。 自 2018 年成立以來,行芯科技始終專注于 EDA(電子設計自動化)簽核領域,致力于填補國產 EDA 技術的空白。憑借著對技術創新的執著追求,行芯科技在底層架構與算

- 專欄行芯PHLEXING

- 19天前

- 319

- 0

- 0

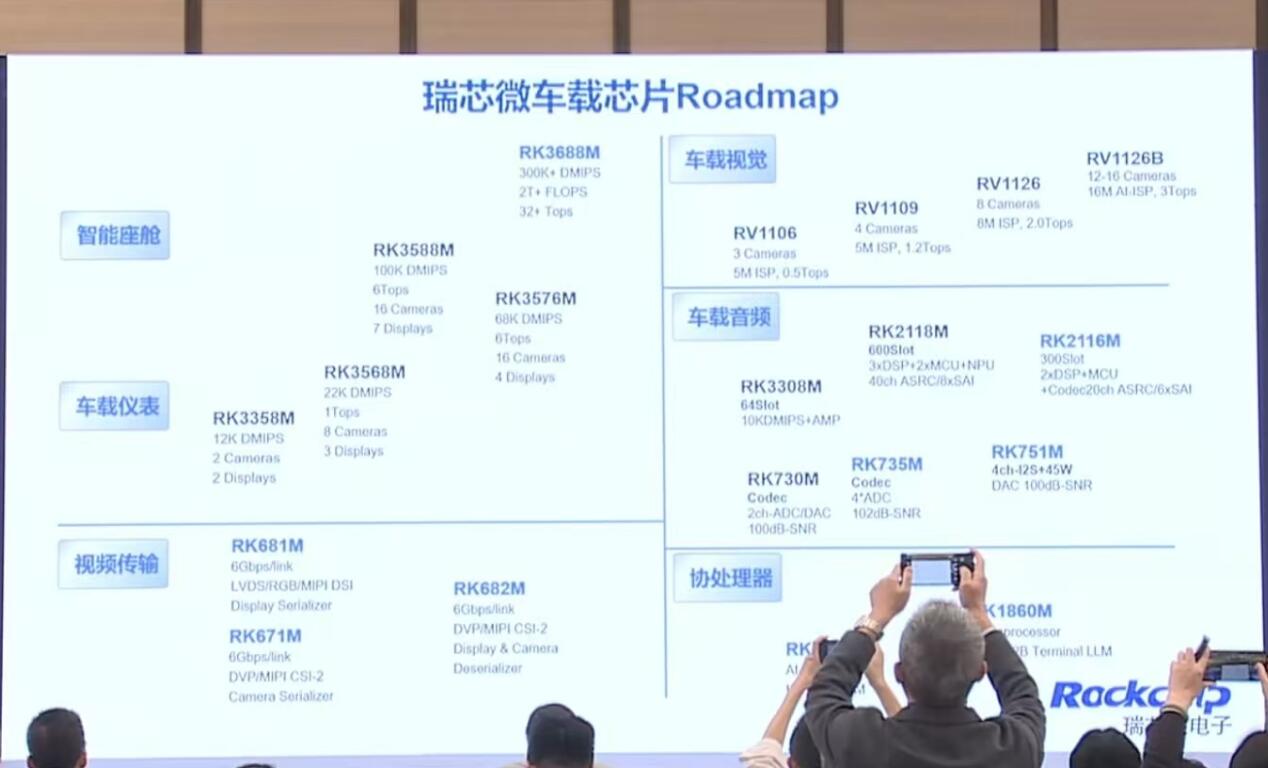

原4nm賽道發力!瑞芯微押注汽車AI SoC,汽車芯片增長前景看好

(電子發燒友報道 文/章鷹)4月26日,在上海車展上舉辦的汽車半導體芯片大會上,瑞芯微車載事業部VP陳楚毅給大家帶來最新的演講《AI芯賦能車載多場景》,他重點介紹了瑞芯微在汽車芯片方面的布局和最新的旗艦產品。 瑞芯微2025年Q1凈利潤大漲209%,AIoT技術優勢延伸到汽車電子領域 瑞芯微2001年成立,2020年在上交所上市。公司產品最早從復讀機、MP4、平板,發展到當前的汽車電子,機器視覺、AIoT,芯片制程也從早期的0.65um,到今天的8nm,每一代都規

- 專欄章鷹觀察

- 21天前

- 3644

- 0

- 0

本土EDA企業英諾達亮相DVcon China 2025

在上周剛剛結束的DVcon China會議上,本土EDA企業英諾達攜其EnAltius昂屹 CDC(ECDC)跨域檢查工具亮相,并發表主題演講《Enhancing CDC tool to deliver complete CDC solutions for advanced IC design》。該工具通過創新算法與全流程覆蓋能力,為高性能芯片設計提供完整的CDC驗證解決方案,顯著提升復雜多時鐘域設計的可靠性與驗證效率。

- 專欄英諾達EnnoCAD

- 24天前

- 270

- 0

- 0

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet和先進封裝通常是互為補充的。Chiplet技術使得復雜芯片可以通過多個相對較小的模塊來實現,而先進封裝則提供了一種高效的方式來將這些模塊集成到一個封裝中。

- 專欄巨霖

- 27天前

- 315

- 0

- 0

Broadcom使用Cadence Spectre FMC Analysis進行時序變化分析

對于最新的微型半導體制作工藝而言,制程工藝變化和器件不匹配帶來了深遠影響。復雜制程工藝也會影響器件生產的可變性,進而影響整體良品率。 蒙特卡洛(MC)仿真使用重復的隨機抽樣方法,將工藝變化與電路性能和功能聯系起來,從而確定它們對良品率的影響。然而,要進行全面的設計空間研究,設計團隊需要完成大量的 MC 仿真才能達到必要的可信度。

- 專欄Cadence楷登

- 29天前

- 1279

- 0

- 0

Cadence解決方案助力高性能傳感器封裝設計

在技術和連通性主宰一切的時代,電子和機械設計的融合將徹底改變用戶體驗。獨立開發器件的時代已經過去;市場對創新、互聯產品的需求推動了業內對協作方法的需求。

- 專欄Cadence楷登

- 29天前

- 1093

- 0

- 0

華大九天版圖寄生參數分析工具Empyrean ADA介紹

在集成電路設計中,寄生參數是決定芯片性能的關鍵因素之一,尤其是在先進工藝節點下,其影響愈發顯著,甚至可能成為影響芯片成敗的決定性因素。

- 專欄華大九天

- 29天前

- 420

- 0

- 0

華大九天牽頭制定車規級EDA團體標準

近日,中國電子工業標準化技術協會正式發布兩項團體標準——《車規級泛模擬集成電路電子設計自動化工具技術要求》(T/CESA 1384-2025)和《車規級平板顯示電路電子設計自動化工具技術要求》(T/CESA 1385-2025)。這兩項標準由華大九天牽頭,聯合行業多家單位共同制定,旨在為車規級EDA的開發和應用提供技術規范,填補國內相關領域標準空白,加速中國新能源汽車產業高質量發展。

- 專欄華大九天

- 29天前

- 1024

- 0

- 0

芯華章以AI+EDA重塑芯片驗證效率

近日,作為國內領先的系統級驗證EDA解決方案提供商,芯華章分別攜手飛騰信息技術、中興微電子在IC設計驗證領域最具影響力的會議DVCon China進行聯合演講,針對各個場景下驗證中的“硬骨頭”問題,用實際案例詮釋“AI+EDA”如何重塑驗證效率,讓大家實實在在的看見國產驗證EDA技術落地的扎實與生態協同創新的力量。

- 專欄芯華章科技

- 1月前

- 394

- 0

- 0