完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > vitis

Vitis Model Composer 是一款 Xilinx 工具包,支持在 MATALB? 和 Simulink? 環(huán)境中進行快速設計探索和驗證,并加速 Xilinx 器件的量產(chǎn)。

文章:149個 瀏覽:7870次 帖子:21個

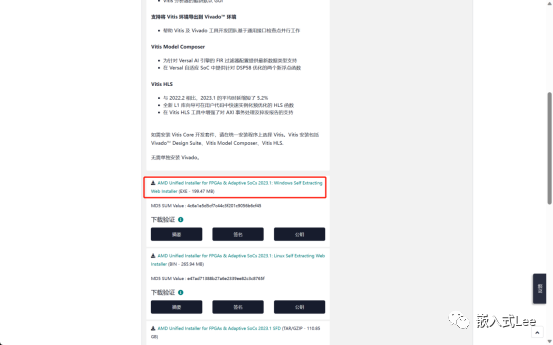

Xilinx提供了一整套開發(fā)環(huán)境用于其FPGA和SOC的開發(fā),主要包括硬件部分和軟件部分的開發(fā)工具,之前硬件部分是vivado軟件部分是sdk,現(xiàn)在統(...

使用Vitis AI在Zynq MP上實現(xiàn)手勢識別

FPGA得益于其高可編程性以及低延遲,低功耗的特點,在機器學習的推理領(lǐng)域已獲得了廣泛的關(guān)注。在過去,F(xiàn)PGA對于軟件開發(fā)人員來說有較高的開發(fā)門檻,把...

如何在Vitis中使用Git集成以及如何使用團隊操作來共享Vitis工程

在上述兩種情況下,用戶始終都能使用 “Refresh Project Models”(刷新工程模型)選項從 Git 倉庫獲取最新更改,在 “System...

閑談Vitis AI|DPU在UltraScale平臺下的軟硬件流程(1)

本篇中,我想跳過一些細枝末節(jié), 先簡單介紹 AMD Xilinx Vitis AI 在 Zynq 這個硬件加速平臺下軟硬件開發(fā)的基本思路和流程,把各個開...

相比于VivadoHLS,Vitis HLS更加智能化,這體現(xiàn)在Vitis HLS可以自動探測C/C++代碼中可并行執(zhí)行地部分而無需人工干預添加prag...

對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之...

這種方法還可以更好地與團隊方法一起使用,并且可以創(chuàng)建可跨多個項目使用的加速內(nèi)核庫(IP)。另一個優(yōu)點是應用于可編程邏輯實現(xiàn)的優(yōu)化駐留在 .xo...

使用AXI4-Lite將Vitis HLS創(chuàng)建的IP連接到PS

在 AXI 基礎第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 ...

自動刪除SDK/Vitis下驅(qū)動程序的舊版本的Linux腳本

Xilinx的開發(fā)工具SDK/Vitis都可以自動根據(jù)Vivado設計,創(chuàng)建軟件工程,自動配置各個外部設備的驅(qū)動程序。為了兼容舊版本工程,SDK/Vit...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題 教程专题

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |