完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > verilog

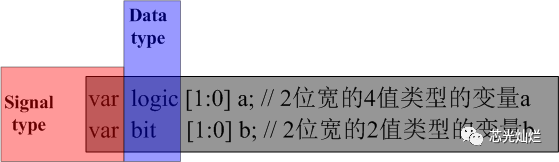

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

文章:1365個(gè) 瀏覽:111790次 帖子:933個(gè)

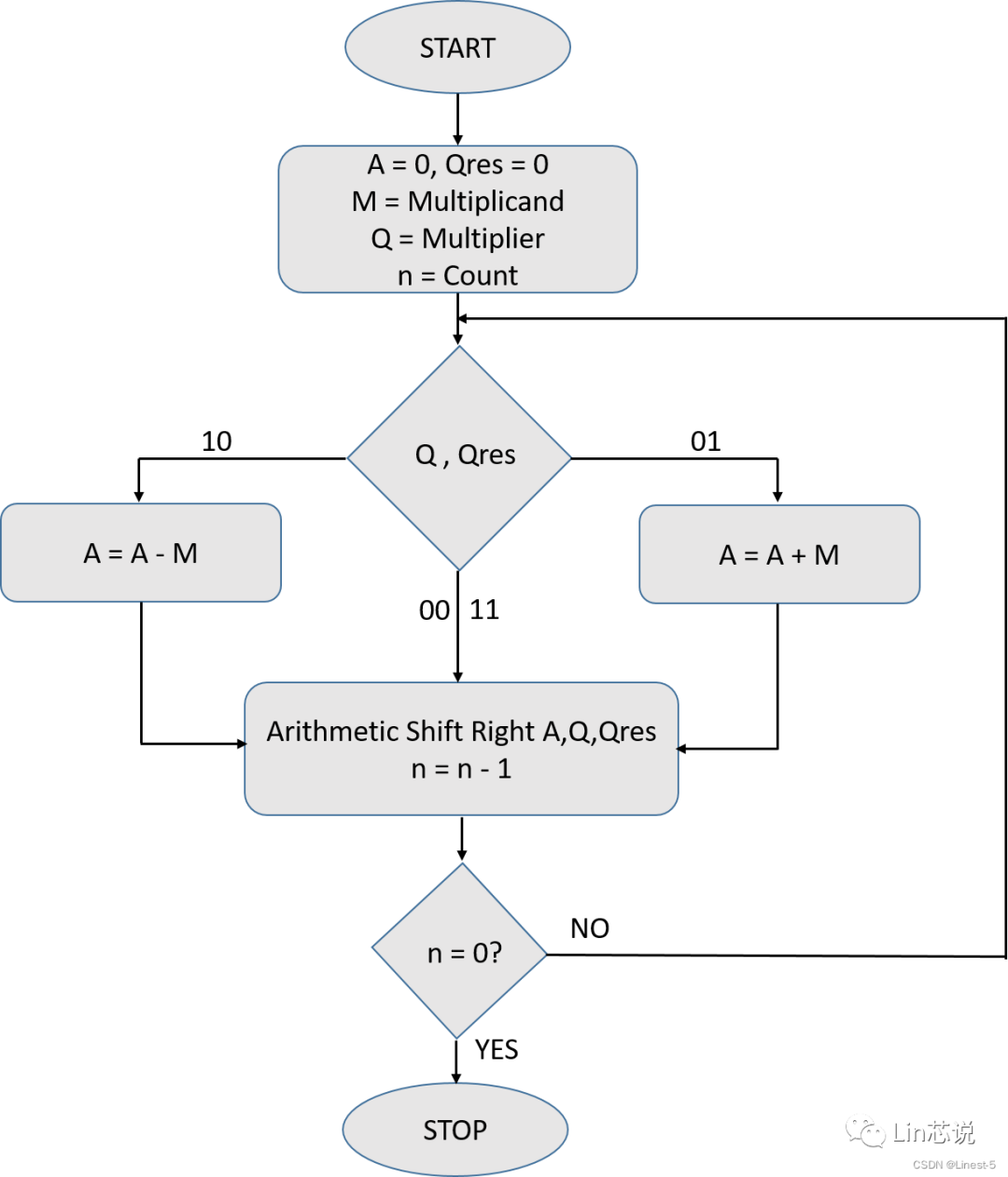

布斯算法(Booth Algorithm)乘法器的Verilog實(shí)現(xiàn)

Booth 的算法檢查有符號二的補(bǔ)碼表示中 'N'位乘數(shù) Y 的相鄰位對,包括低于最低有效位 y?1 = 0 的隱式位。

相信不少人都聽過verilog這個(gè)詞,今天我就想講一講我所理解的verilog是什么。

2023-12-04 標(biāo)簽:寄存器芯片設(shè)計(jì)Verilog 1546 0

Verilog代碼:if-else和case的電路結(jié)構(gòu)和區(qū)別

每個(gè)if-else就是一個(gè)2選1mux器。當(dāng)信號有明顯優(yōu)先級時(shí),首先要考慮if-else,但是if嵌套過多也會(huì)導(dǎo)致速度變慢;if語句...

如何設(shè)計(jì)一個(gè)參數(shù)化的數(shù)據(jù)選擇器

在FPGA設(shè)計(jì)中,大部分情況下我們都得使用到數(shù)據(jù)選擇器。并且為了設(shè)計(jì)參數(shù)化,可調(diào),通常情況下我們需要一個(gè)參數(shù...

2023-11-20 標(biāo)簽:FPGA設(shè)計(jì)Verilog數(shù)據(jù)選擇器 1420 0

消失了好久,沒有寫文章,也沒有做筆記,因?yàn)樽罱仝s一個(gè)比賽,時(shí)間很緊,昨天周六終于結(jié)束了,所以趁著周末這會(huì)兒有時(shí)間,寫點(diǎn)東西,記錄...

基于Feature架構(gòu)設(shè)計(jì)的百兆以太網(wǎng)交換機(jī)項(xiàng)目

第二代交換機(jī)有更豐富的feature,更貼近真正使用的功能,除rtl代碼,詳細(xì)設(shè)計(jì)文檔外,還會(huì)包括驗(yàn)證環(huán)境、驗(yàn)證代碼,最后項...

現(xiàn)在公司里做設(shè)計(jì)是用SV還是Verilog?

數(shù)字電路設(shè)計(jì)主要就是,選擇器、全加器、比較器,乘法器,幾個(gè)常用邏輯門,再加個(gè)D觸發(fā)器,電路基本都能實(shí)現(xiàn)了。

CRC校驗(yàn)碼的多種Verilog實(shí)現(xiàn)方式

該CRC-8的生成多項(xiàng)式為G(D)=D8+D2+D+1,對CRC進(jìn)行簡化表示時(shí)可以忽略最高位的D8,結(jié)合圖示中三個(gè)異或運(yùn)算的位置更容易理解...

Verilog基礎(chǔ):介紹幾個(gè)常用的按位操作符

位操作符是對二進(jìn)制位進(jìn)行操作的運(yùn)算符。以下是一些常用的位操作符

2023-11-09 標(biāo)簽:Verilog狀態(tài)機(jī)XOR 2318 0

位操作符是對二進(jìn)制位進(jìn)行操作的運(yùn)算符。

2023-11-09 標(biāo)簽:二進(jìn)制計(jì)算機(jī)網(wǎng)絡(luò) 1781 0

如何高效替換Soft IP中的標(biāo)準(zhǔn)cell

我們在購買soft IP的時(shí)候,vendor提供的是通用的verilog/system verilog的代碼,而在不同的項(xiàng)目中,我們采用的工藝不一樣,因...

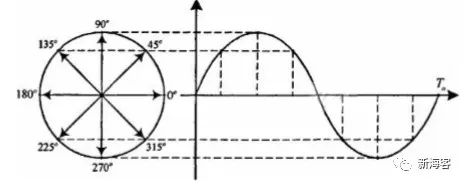

DDS信號生成模塊的Verilog實(shí)現(xiàn)

直接數(shù)字頻率合成器(Direct Digital Synthesizer,DDS),是一種頻率合成技術(shù),具有相對帶寬大、頻率轉(zhuǎn)換速度快、相位分辨率高、連...

使用“~”運(yùn)算符對單bit信號進(jìn)行取反(也稱為位翻轉(zhuǎn)或反向)。

2023-11-08 標(biāo)簽:Verilogfor循環(huán) 1793 0

使用枚舉類型表示狀態(tài)機(jī)進(jìn)入死循環(huán)

在定義狀態(tài)機(jī)中的狀態(tài)時(shí),除了可以使用宏(define)或者參數(shù)(parameter)聲明定義外,還可以使用枚舉類型

是通過DPI實(shí)現(xiàn)SV和C的交互,然后用 SV的task將C的數(shù)據(jù)轉(zhuǎn)成對應(yīng)的總線數(shù)據(jù)下發(fā)到各個(gè)外設(s...

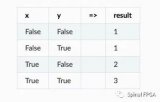

無論是SystemVerilog還是SpinalHDL,都有Last valid assignment wins的語法特征。如在SpinalHDL-Do...

2023-11-04 標(biāo)簽:VerilogCache狀態(tài)機(jī) 851 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題 教程专题

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |