完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > ddr

DDR=Double Data Rate雙倍速率同步動態(tài)隨機(jī)存儲器。嚴(yán)格的說DDR應(yīng)該叫DDR SDRAM,人們習(xí)慣稱為DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的縮寫,即同步動態(tài)隨機(jī)存取存儲器。

文章:513個 瀏覽:66346次 帖子:533個

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數(shù)據(jù)

PL和PS的高效交互是zynq soc開發(fā)的重中之重,我們常常需要將PL端的大量數(shù)據(jù)實(shí)時送到PS端處理,或者將PS端處理結(jié)果實(shí)時送到PL端處理,...

ZYNQ擁有ARM+FPGA這個神奇的架構(gòu),那么ARM和FPGA究竟是如何進(jìn)行通信的呢?本章通過剖析AXI總線源碼,來一探其中的秘密。

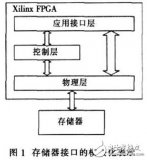

基于Xilinx FPGA實(shí)現(xiàn)的DDR SDRAM控制器工作過程詳解

在高速信號處理系統(tǒng)中, 需要緩存高速、大量的數(shù)據(jù), 存儲器的選擇與應(yīng)用已成為系統(tǒng)實(shí)現(xiàn)的關(guān)鍵所在。DDR SDR...

DDR4(第四代雙倍數(shù)據(jù)速率同步動態(tài)隨機(jī)存取存儲器)是一種高帶寬的存儲器,今天主要講述一下DDR4在Layout過程中的一些細(xì)節(jié)。在DDR的設(s...

DDR、DDR2、DDR3、DDR4、LPDDR的區(qū)別

DDR是Double Data Rate的縮寫,即“雙倍速率同步動態(tài)隨機(jī)存儲器”。DDR是一種技術(shù),中國大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDR....

2023-07-16 標(biāo)簽:數(shù)據(jù)傳輸比較器DDR 1.2萬 0

顯存的發(fā)展歷史,展望下一代GDDR6顯存的一些新特性

QDR(Quad Data Rate):四倍數(shù)據(jù)倍率,在DDR的基礎(chǔ)上,擁有獨(dú)立的寫接口和讀接口,以此達(dá)到4倍速率,例如QDR-SRAM等 。DDR2-.....

講解全志國產(chǎn)處理器T113-i與T113-S3的不同之處!

而T113-S3在不加散熱片情況下,工作溫度范圍較小(-25℃ ~ +75℃),并非真工業(yè)級。即使加了散熱片,T113-S3工作溫度范圍(-25℃ ~ ...

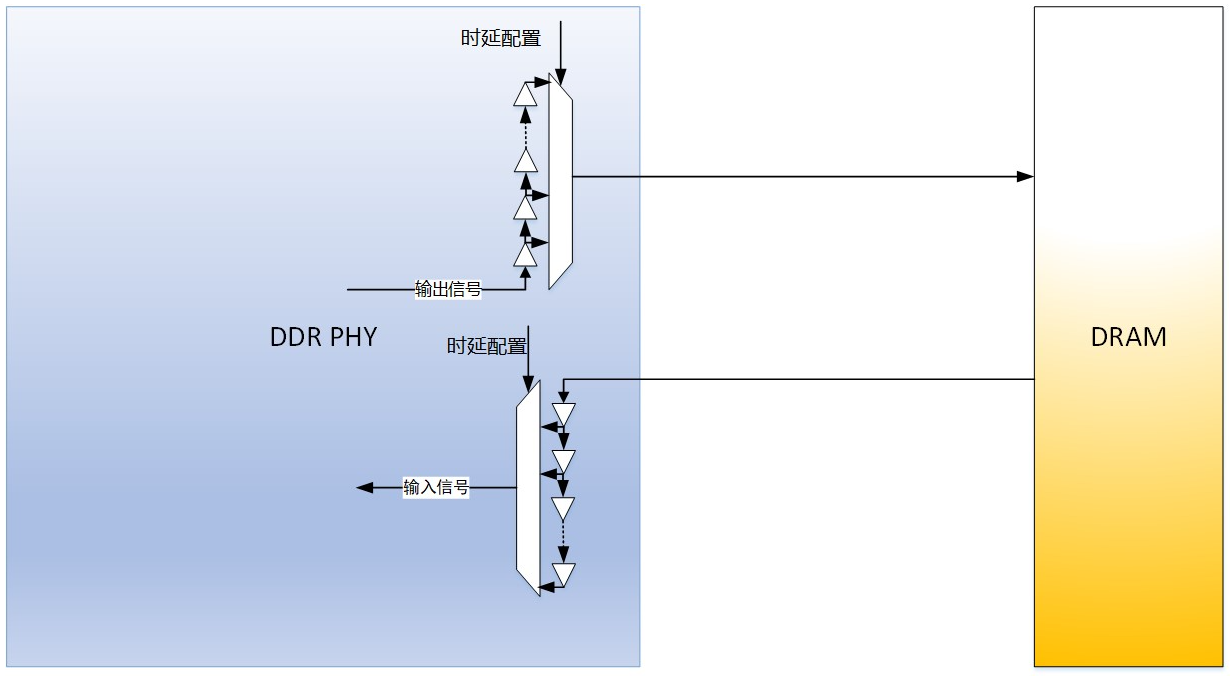

芯耀輝軟硬結(jié)合的智能DDR PHY訓(xùn)練技術(shù)

在實(shí)際的應(yīng)用中,命令(command)路徑上的延時會超過數(shù)據(jù)(DQ)路徑的延時。假設(shè)路徑差值 = 命令路徑延時 – 數(shù)據(jù)路徑延時,一...

DDR、DDR2、DDR3、DDR4、LPDDR區(qū)別

DDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺...

CFM與CC各有優(yōu)缺點(diǎn),CFM的校正速度快,僅用兩個時鐘周期,但容易受到噪音干擾,如果測量失誤,則內(nèi)部的延遲就永遠(yuǎn)錯下去。CC的優(yōu)點(diǎn)則...

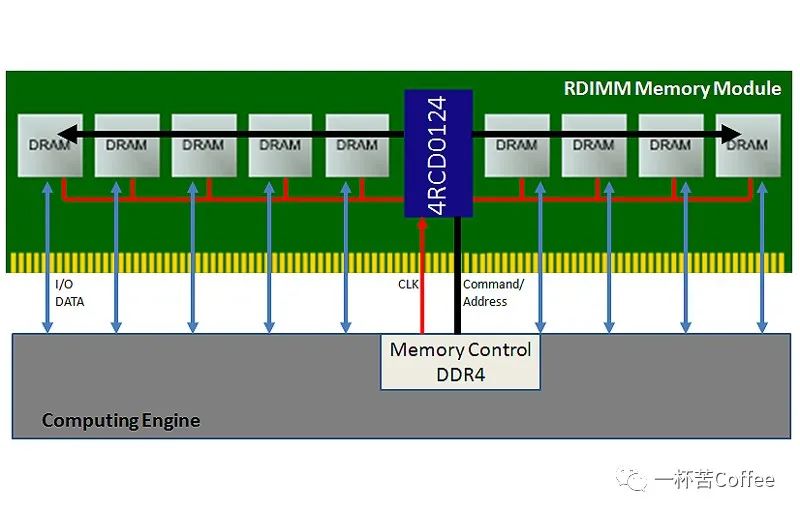

DDR 正面就是一個rank,背面如果也有顆粒,那就又是一個rank。實(shí)物圖中的8個顆粒組成了一個rank。

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第十章】DDR3讀寫測試實(shí)驗(yàn)

本實(shí)驗(yàn)為后續(xù)使用DDR3內(nèi)存的實(shí)驗(yàn)做鋪墊,通過循環(huán)讀寫DDR3內(nèi)存,了解其工作原理和DDR3控制器的寫法,由于DDR3控...

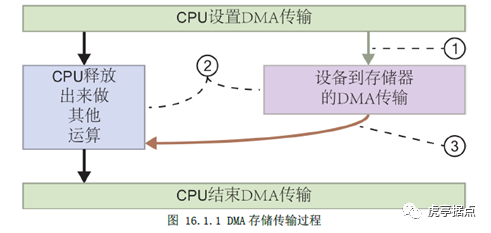

DMA是一種內(nèi)存訪問技術(shù),允許某些計算機(jī)內(nèi)部的硬件子系統(tǒng)可以獨(dú)立的直接讀寫內(nèi)存,而不需要CPU介入處理,從而不需要CPU的大量中斷負...

關(guān)于Prefetch和Burst相關(guān)的內(nèi)容

可以發(fā)現(xiàn),Column Address的A2,A1,A0三位被用于Burst Order功能,并且A3也被用于Burst Type功能。由于一般情況,我...

這樣一來,信號完整性就會受到不同程度的影響,為了能夠保持等效電阻一致,我們希望ODT的RTT(終結(jié)電阻)是可以動態(tài)修改的,而不需要每次都要通過MRS C...

PS_CLK:系統(tǒng)晶振的時鐘,這個是PS端的的時鐘來源,經(jīng)過一個叫PLL的鎖相環(huán)功能部件,輸出到ARM PLL和I/O PLL以及DDR PLL,后續(xù)的.....

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題 教程专题

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |