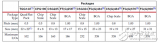

Critical Link公司的某客戶需要針對多個應(yīng)用開發(fā)一個擴頻無線電收發(fā)器。該客戶已經(jīng)開發(fā)出一套算法,準備用于對信號進行調(diào)制和解調(diào),但他們卻缺少構(gòu)建完整系統(tǒng)的資源和專業(yè)知識。客戶希望利用軟件定義無線電(SDR)系統(tǒng)的靈活性優(yōu)勢。本文將探討如何基于德州儀器(TI)的OMAP-L138 DSP+ARM處理器與FPGA來實現(xiàn)該系統(tǒng)。平臺Critical Link選擇其MityDSP-L138F嵌入式系統(tǒng)模塊作為SDR的基礎(chǔ),因為該模塊不僅具有很強的處理能力,而且可以為客戶節(jié)省大量的預(yù)先設(shè)計成本。MityDSP-L138F模塊具有一個TI的OMAP-L138DSP+ARM處理器,該處理器集成了一個456MHz ARM9處理內(nèi)核和一個456MHz TMS320C674x DSP內(nèi)核。此外,該模塊還包含了Xilinx公司的Spartan-6 LX16 FPGA、NAND和NOR閃存以及DDR2存儲器。出于原型考慮,該設(shè)計使用了TI針對無線電的高速ADC與DAC評估套件。此外,它還需要能夠在60MHz采樣頻率轉(zhuǎn)換的數(shù)據(jù)轉(zhuǎn)換器。針對A/D轉(zhuǎn)換器,該設(shè)計選用了TI的ADS5562。該轉(zhuǎn)換器具有16位精度,可以以80Msps采樣速率進行轉(zhuǎn)換。因為擴頻無線電需要將信號從背景噪聲中抽離,所以高動態(tài)范圍對于這種無線電來說非常重要。對于DAC,該平臺選用了TI的THS5671。這是一款14位125Msps差分電流輸出DAC。負責(zé)本項目的客戶為該系統(tǒng)提供的前端設(shè)計如圖所示。?[[wysiwyg_imageupload:454:]]圖:客戶提供的前端設(shè)計。數(shù)據(jù)傳送問題許多基于DSP的應(yīng)用要求具有高速數(shù)據(jù)傳輸功能,以使系統(tǒng)能夠采集和處理數(shù)據(jù),或者將數(shù)據(jù)傳送到外設(shè)。通常,數(shù)字信號處理器都包含了異步地址/數(shù)據(jù)總線,以使處理器能夠讀寫外設(shè)。這些接口可以滿足低速傳送數(shù)據(jù)的要求,但是在高速情況下卻會成為瓶頸。OMAP-L138 DSP+ARM處理器具有一個稱為外部存儲器接口A(EMIFA)的地址/數(shù)據(jù)總線。EMIFA允許對外部存儲器或設(shè)備進行異步尋址,并含有若干控制引腳,以滿足不同等待狀態(tài)和傳輸寬度等等要求。因為該接口具有很強的通用性,所以每次事務(wù)處理都可以利用多個時鐘周期來完成。例如,最小的讀取周期需要每16位3個周期。在100MHz下運行EMIFA,假設(shè)總線上沒有其他數(shù)據(jù),可得到的數(shù)據(jù)傳輸速率最大為66MB/s。在總線上進行交錯讀寫會顯著地降低傳輸速率,因為這必須增加額外的轉(zhuǎn)換周期。OMAP-L138處理器還包括了一個更為專用的接口,即通用并行端口(uPP)。該接口專門用來將大量數(shù)據(jù)連續(xù)送入處理器內(nèi)存或從其中讀出。uPP的傳輸速率為每時鐘周期1個數(shù)據(jù)字(8位或16位);或者針對雙數(shù)據(jù)速率為每時鐘周期2個數(shù)據(jù)字,但是時鐘速率必須減半。uPP時鐘速率可以高達處理器時鐘速率的一半。對于在300MHz下運行的OMAP-L138處理器,uPP時鐘可以達到75MHz。這使吞吐量可以達到150MB/s。OMAP-L138處理器實際包括2個uPP接口,每個都可以單獨配置。這允許我們?yōu)閼?yīng)用建立一個傳輸端口和一個接收端口,從而消除單一總線上的資源爭用問題。從硬件角度看,uPP接口是一種非常簡單的同步數(shù)據(jù)接口。它包含一個時鐘引腳、數(shù)據(jù)引腳和若干控制引腳,用于指明有效數(shù)據(jù)和起始/等待條件。事實上,該接口可以與一些并行ADC和DAC實現(xiàn)無縫連接。架構(gòu)因為我們的SDR需要與DSP之間進行高速數(shù)據(jù)傳送,所以我們選擇使用uPP端口來實現(xiàn)FPGA接口。我們使用一個端口作為接口的發(fā)送端,使用另一端口作為接收端。事實上,該處理系統(tǒng)可以同時進行發(fā)送和接收,盡管這并非系統(tǒng)要求。這個功能的優(yōu)勢在于,它允許我們在發(fā)送器和接收器之間建立循環(huán),以進行大量的測試和調(diào)試工作。對于一個10MHz載波來說,這種調(diào)制所需的處理特性,使系統(tǒng)過多地將全部處理任務(wù)在OMAP-L138處理器的DSP中完成。在速度較慢的應(yīng)用中,DSP可以單獨滿足數(shù)據(jù)速率的要求,但由于客戶要求以更高的速率發(fā)送數(shù)據(jù),所以我們需要使用FPGA來執(zhí)行部分處理任務(wù)。FPGA尤其擅長以非常高的頻率執(zhí)行重復(fù)任務(wù),因此,我們選擇在FPGA中執(zhí)行初始解調(diào)和基帶處理。這樣,我們就可以大量減少DSP中的數(shù)據(jù)并降低DSP的數(shù)據(jù)速率。在發(fā)送側(cè),DSP可以預(yù)先計算最終的射頻信號,以便將有效負載數(shù)據(jù)的編碼時間降至最短。因此,F(xiàn)PGA僅僅將發(fā)送波形數(shù)據(jù)從uPP端口發(fā)送到DAC。事實上,不使用FPGA也可以完成這項工作,但是我們在設(shè)計系統(tǒng)時仍將FPGA加入,以便在需要時使用。FPGA的雙端口RAM中包含一個正弦或余弦查找表,用于合成接收機的本機振蕩器信號。FPGA中的乘法器/累加器用于根據(jù)要求解調(diào)信號。發(fā)送處理鏈當(dāng)ARM微處理器上的軟件向DSP發(fā)出傳輸消息包時,發(fā)送過程將會啟動。DSP對數(shù)據(jù)進行編碼,使其成為擴頻調(diào)制序列,并將其編入一個預(yù)先計算的已調(diào)制正弦波查找表。然后,DSP使用uPP的內(nèi)置DMA引擎建立一個DMA傳輸,用以將數(shù)據(jù)從DSP存儲器傳送到DAC。FPGA則起到中間調(diào)解作用,負責(zé)向DAC和uPP提供可編程時鐘,用于設(shè)置發(fā)送采樣率。接收處理鏈接收流程連續(xù)運行。ADC樣本被同步送入FPGA——通過將輸入樣本與正交正弦和余弦波形相乘并積分,對數(shù)據(jù)進行基帶處理,從而以較低的數(shù)據(jù)速率向DSP提供同相和正交樣本。這些樣本被uPP DMA引擎以DMA方式送入DSP存儲器,再由DSP處理剩余的擴頻解調(diào)處理步驟。一旦信號被解調(diào),得到的數(shù)據(jù)包將使用TI的DSPLink處理器之間通信庫傳送回ARM處理器。ARM軟件接收解碼數(shù)據(jù),并通過命令接口將數(shù)據(jù)呈現(xiàn)給用戶。使用FPGA執(zhí)行接收器初始基帶處理能夠釋放足夠的DSP處理能力,從而輕松完成剩余的解調(diào)和解碼工作。如果系統(tǒng)中的輸入信號采樣率顯著低于60MHz,則DSP可不借助FPGA的力量,獨自執(zhí)行基帶處理任務(wù)。該系統(tǒng)的初始工作使用了一個低頻段(幾十或幾百kHz)的載頻。在初始實施過程中,F(xiàn)PGA僅負責(zé)將數(shù)據(jù)發(fā)送至DSP,由DSP執(zhí)行所有的解調(diào)功能。這種方式很奏效,但是無法達到更高采樣率應(yīng)用的要求。通過在FPGA中實施基帶處理,我們可以在全采樣率下進行數(shù)字基帶處理和濾波,從而改善系統(tǒng)的噪聲性能:這在欠采樣下是無法做到的。本文小結(jié)該項目實現(xiàn)的原型系統(tǒng)已經(jīng)為多個應(yīng)用實施過概念驗證。與理想擴頻無線電的理論性能相比,該系統(tǒng)的性能非常優(yōu)異。TI OMAP-L138 DSP+ARM處理器與FPGA的結(jié)合,實現(xiàn)了具有出色性能的高性價比解決方案。將DSP的部分處理負載分配給FPGA,使系統(tǒng)可以使用低成本、低功耗的處理器來構(gòu)建,而不是由GHz級的DSP處理所有工作。uPP接口支持簡單的FPGA接口功能,并且與其他可用的DSP接口相比,具有明顯的性能優(yōu)勢。使用uPP中的DMA進行數(shù)據(jù)傳送,可以進一步釋放DSP資源,將DSP周期用于更加重要的工作。在OMAP-L1x平臺中加入ARM處理器后,便可使用嵌入式Linux提供通信基礎(chǔ)設(shè)施,來管理系統(tǒng)中的用戶界面和所有的內(nèi)務(wù)處理功能。此外,使用SD卡、USB驅(qū)動器或者以太網(wǎng)連接,可以對系統(tǒng)軟件(ARM、DSP和FPGA)進行現(xiàn)場升級。因此,SDR系統(tǒng)的靈活性可以充分滿足處理算法的發(fā)展要求。David A. Rice技術(shù)總監(jiān)Critical LinkJoseph Coombs應(yīng)用工程師德州儀器

基于DSP和賽靈思Spartan-6的SDR系統(tǒng)設(shè)計與實現(xiàn)

- dsp(343841)

- SDR(50129)

相關(guān)推薦

Spartan-6 FPGA是否需要設(shè)計中的上電復(fù)位電路

您好Xilinx社區(qū),有人能否就Spartan-6 FPGA是否需要設(shè)計中的上電復(fù)位電路給出明確的答案?在附圖中,我們的設(shè)計中有這個上電復(fù)位電路。然而,我們遇到了電路問題,并決定在我們的設(shè)計中將

2019-04-18 10:15:45

Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B的差異是什么

嗨,我想知道是否有關(guān)于它們之間[fly]的差異的[/fly]技術(shù)文檔Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B看起來,差異是芯片修訂版

2019-07-02 10:45:31

Spartan-6器件的可用性

有誰知道更多關(guān)于Spartan-6 XC6SLX150的可用性?我知道周圍有工程樣品,但我無法獲得最終商業(yè)版的任何交貨時間。謝謝,羅伯特以上來自于谷歌翻譯以下為原文Anyone knows more

2019-05-24 13:15:09

Spartan-6的QDR接口能連接到MCB引腳嗎

親愛的論壇,我正在處理將** II SRAM連接到Spartan-6 FPGA的問題。我不是斯巴達IP核的專家,但我意識到Spartan-6沒有預(yù)見到的QDR接口。但是我確信它可以做到。我遇到的唯一

2019-05-22 07:16:30

Spartan 6是否支持SDR SDRAM?

嗨,Spartan 6是否支持SDR SDRAM(單數(shù)據(jù)輻射SDRAM)?在ISE存儲器接口生成器中,沒有選擇SDR SDRAM的選項。有沒有辦法在斯巴達6中使用SDR SDRAM

2019-04-16 09:33:03

Spartan-3A與Spartan-3AN 低成本誰更有優(yōu)勢?

設(shè)計的CCD線陣相機,基于FPGA的,現(xiàn)在選用一款低成本的賽靈思的FPGA芯片,Spartan-3A與Spartan-3AN到底用哪款好呢?

2014-04-02 11:23:40

賽靈思7系列采用FPGA電源模塊

。ROHM與安富利公司共同開發(fā)賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評估套件Mini-Module Plus 用的電源模塊。安富利公司已經(jīng)開發(fā)出多款賽靈思

2018-12-04 10:02:08

賽靈思Spartan開發(fā)板使用困境記錄 精選資料分享

賽靈思Spartan開發(fā)板使用困境記錄原理圖和接口主要是對照核心板的原理圖,一般的接法就是賽靈思系列的單片機,連接好電源和下載器,記得預(yù)先安好驅(qū)動,驅(qū)動安裝成功與否能夠在設(shè)備管理器處查看。作者困境

2021-07-13 08:42:10

賽靈思FPGA原理圖例子之s3astarter

`賽靈思FPGA原理圖例子之s3astarter 賽靈思一向是FPGA領(lǐng)域里的領(lǐng)先者,運用FPGA需要深入的理解它的工作原理,小編親子整理了s3astarter 的經(jīng)典fpga原理圖分享給電子工程師們。賽靈思FPGA原理圖例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

賽靈思FPGA對DLP數(shù)字影院投影儀產(chǎn)生了哪些影響?

賽靈思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP數(shù)字影院投影儀產(chǎn)品,均采用了賽靈思Virtex?-5 FPGA系列產(chǎn)品。

2019-08-19 07:12:03

賽靈思FPGA該怎么應(yīng)對內(nèi)窺鏡系統(tǒng)架構(gòu)的挑戰(zhàn)?

什么是賽靈思FPGA?如何幫助內(nèi)窺鏡制造商克服復(fù)雜的設(shè)計約束,生產(chǎn)出極具競爭優(yōu)勢的產(chǎn)品?如何幫助他們成功構(gòu)建外形小巧的低功耗內(nèi)窺鏡攝像頭、高性價比的攝像機控制單元(CCU),以及多功能、低成本的圖像管理設(shè)備?

2019-09-17 06:31:55

電子發(fā)燒友App

電子發(fā)燒友App

評論