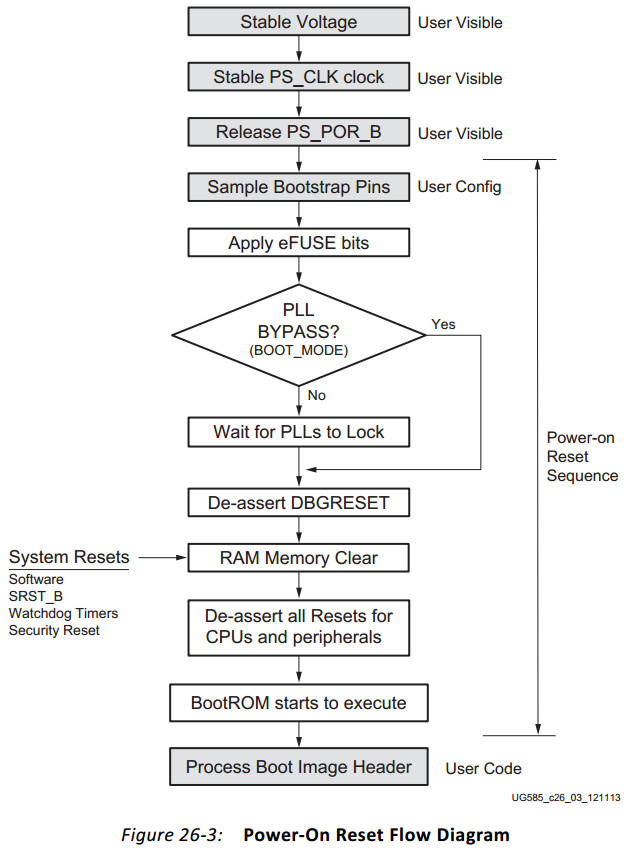

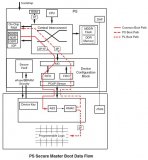

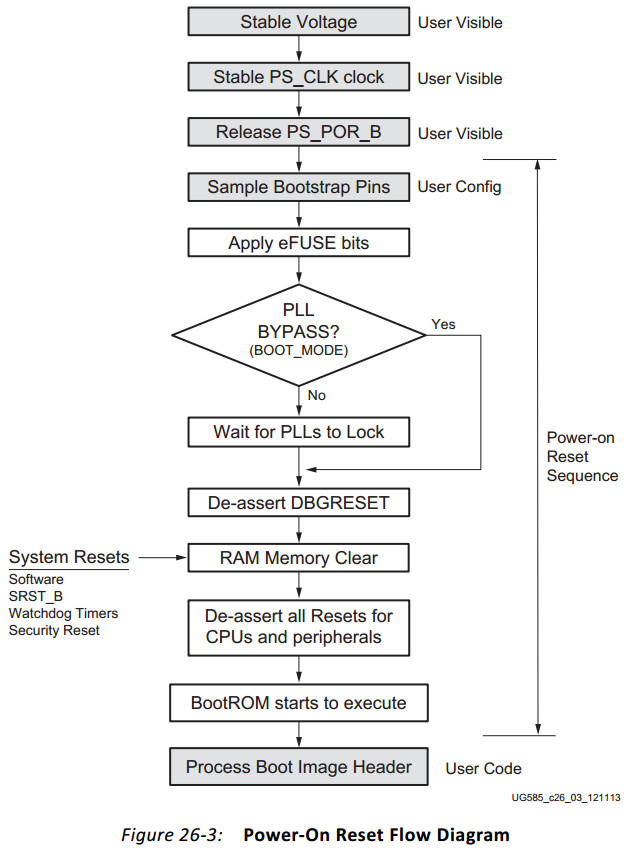

本文主要介紹zynq啟動(dòng)過程,主要包括BootROM和FSBL等的執(zhí)行過程。 硬件啟動(dòng)過程 1. 重新上電或POR復(fù)位后進(jìn)行硬件啟動(dòng)過程 2. 掃描啟動(dòng)引腳設(shè)置,并存入只讀寄存器

2020-11-23 14:53:52 8313

8313

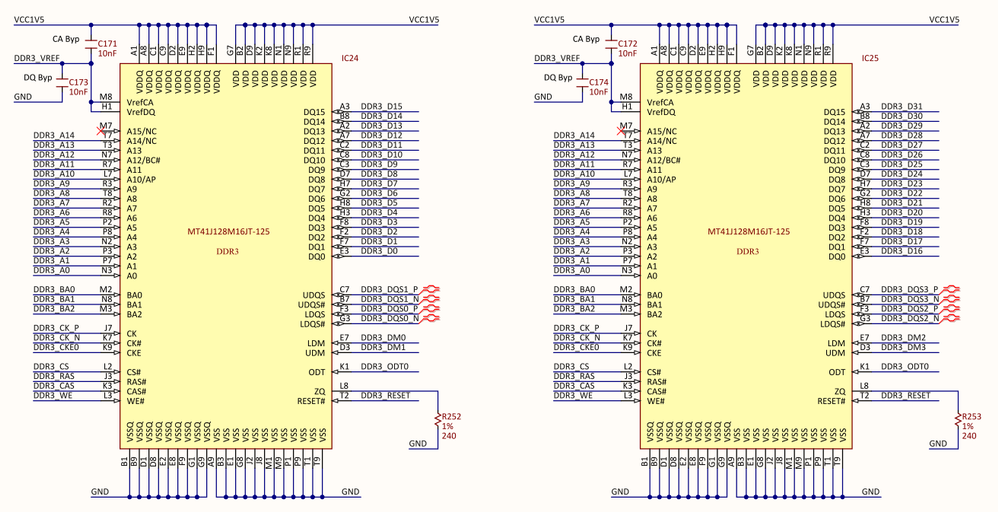

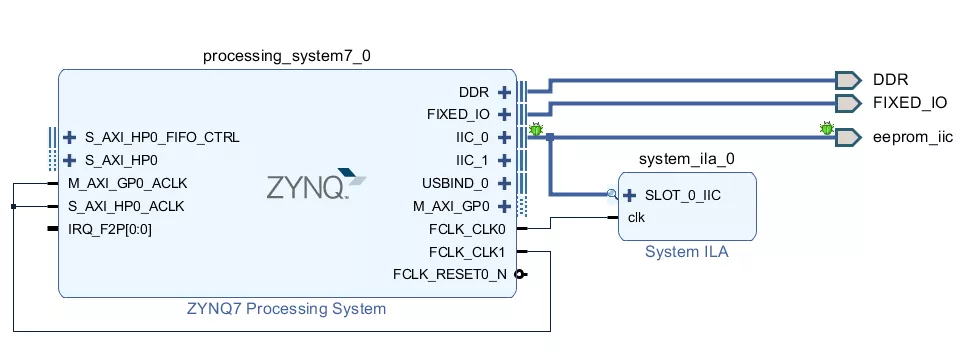

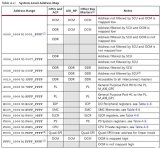

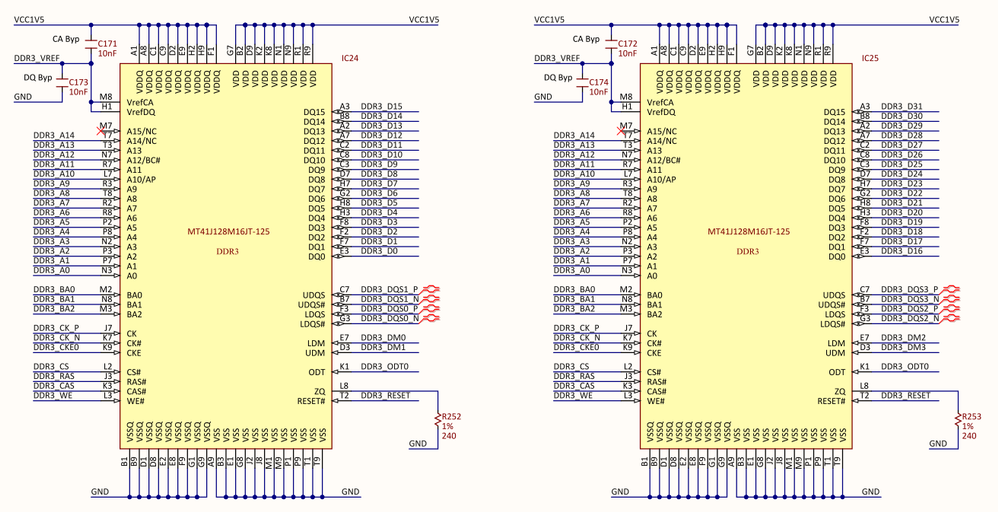

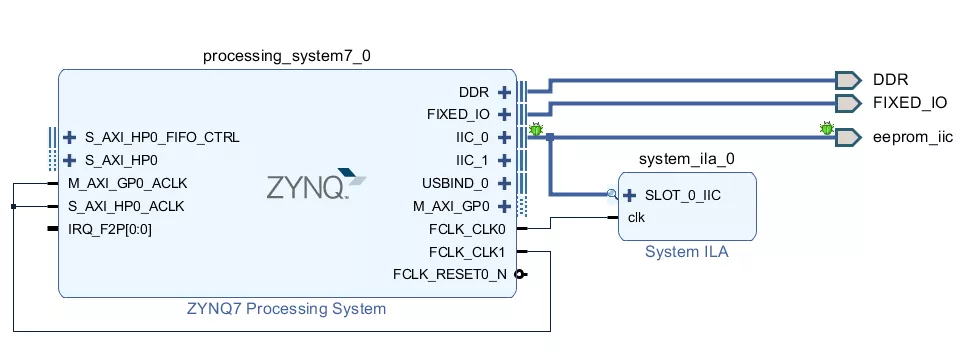

Controller接口,如果外部硬件連接了DDR器件,于是在ZYNQ Processing System中正確配置了相應(yīng)的信號(hào)和參數(shù)后,DDR就可以成為ZYNQ的內(nèi)存,在SDK中可以直接使用memcpy

2020-11-27 12:18:15 6687

6687

基于zynq7020器件來搭建Linux系統(tǒng),描述搭建Linux系統(tǒng)過程中PL側(cè)的配置以及對(duì)u-boot,kenel,桌面系統(tǒng)的配置和

2020-11-30 11:56:01 3490

3490

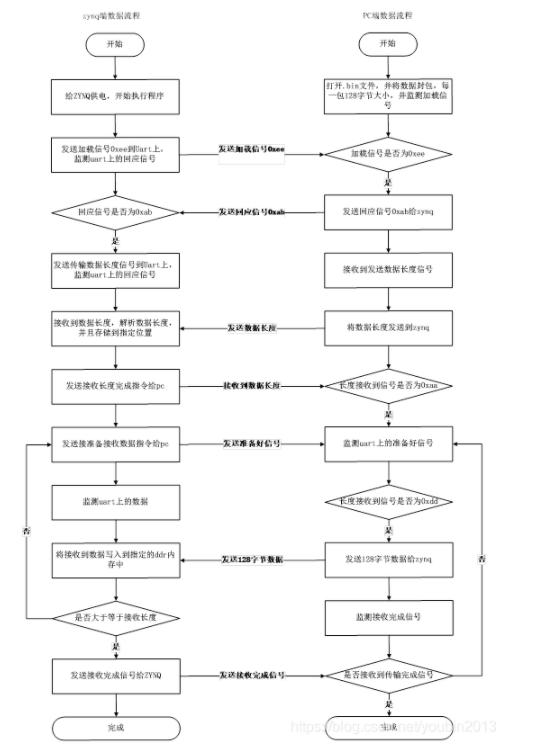

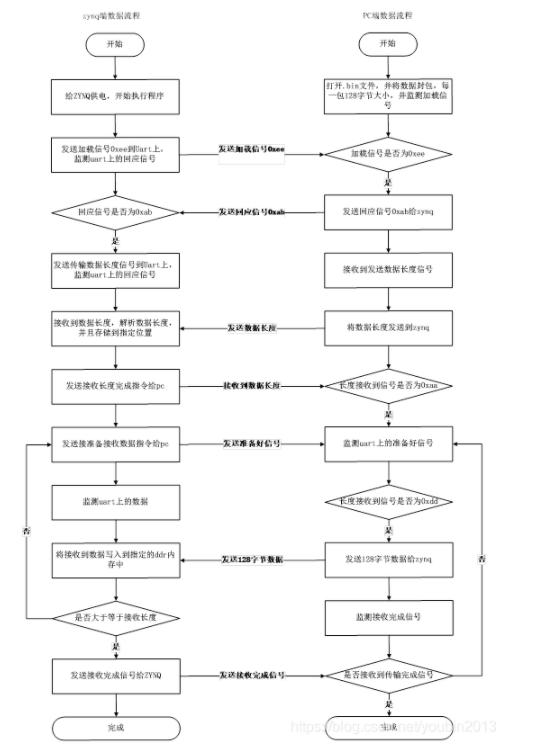

加載方法 ZYNQ的啟動(dòng)鏡像是由FSBL程序(bootloader),PL配置文件(硬件比特流文件),應(yīng)用層軟件三個(gè)部分組成,其通過SDK的軟件生成工具把三個(gè)部分按規(guī)定的格式拼湊成一個(gè).bin文件

2020-12-05 10:15:37 4952

4952

Zynq可擴(kuò)展處理平臺(tái)是賽靈思新一代 FPGA的可編程技術(shù)的產(chǎn)品系列。與采用嵌入式處理器的FPGA不同,Zynq產(chǎn)品系列的處理系統(tǒng)不僅能在開機(jī)時(shí)啟動(dòng),而且還可根據(jù)需要配置可編程邏輯。采用這種方法

2020-12-25 14:15:48 5212

5212 Zynq-7000AP SOC器件有效利用了片上CPU來幫忙配置,在沒有外部JTAG的情況下,處理系統(tǒng)(PS)與可編程邏輯(PL)都必須依靠PS來完成芯片的初始化配置。 ZYNQ的兩種啟動(dòng)模式:從BootROM主動(dòng)啟動(dòng),從JTAG被動(dòng)啟動(dòng)。

2023-08-02 09:33:09 736

736

在 AMD SoC 器件(AMD Zynq 7000 SoC,AMD Zynq UltraScale+ MPSoC,AMD Versal Adaptive SoC),常見的啟動(dòng)方式是通過加載外部

2023-12-22 10:27:25 506

506

51一樣應(yīng)用,那么你可以參考一下。參考文章EBAZ4205 ZYNQ 7Z010 裸機(jī)程序NAND固化 JTAG調(diào)試方法如果本文有地方寫的不清楚可以跳轉(zhuǎn)過去看下。本文主要是硬件改動(dòng),軟件燒錄與測(cè)試方法與參考文章并無區(qū)別。可以先看完本文的硬件改動(dòng)后再看參考文章,改動(dòng)的地方主要是原理圖中標(biāo)紅色框的這兩個(gè)電阻(

2022-01-06 07:52:41

User Defined文件夾處右擊,并在彈出的菜單中點(diǎn)擊“New Target Configuration”新建目標(biāo)配置文件:在打開的目標(biāo)配置文件中,需要配置仿真器類型、器件型號(hào),我們實(shí)驗(yàn)用的仿真器為

2023-02-21 14:51:50

本帖最后由 一語奔馳 于 2016-11-25 15:18 編輯

我ZYNQ外接的PHY是88E1512,現(xiàn)在有一個(gè)系統(tǒng),外接的是88E1510的PHY,但是我想使用88E1512來實(shí)現(xiàn)光口

2016-11-25 14:21:28

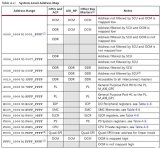

ZYNQ 分為 PS 和 PL 兩部分,那么器件的引腳(Pin)資源同樣也分成了兩部分。ZYNQ PS 中的外設(shè)可以通過 MIO(Multiuse I/O,多用輸入/輸出)模塊連接到 PS 端的引腳

2022-02-08 07:27:16

XinesC6657.gel。設(shè)置完Gel文件后,點(diǎn)擊Save: 1.1.3.2.2.2 啟動(dòng)目標(biāo)配置文件在已經(jīng)創(chuàng)建并設(shè)置好的目標(biāo)配置文件處右擊,并在彈出的菜單中點(diǎn)擊Launch Selected Configuration

2023-02-02 21:43:20

說一下配置的過程,如何從PDF中拿出參數(shù)來首先看一下Zynq MPSoC支持的DDR,這里的手冊(cè)是UG1085,首先是最大支持多少

2022-04-19 17:56:03

Zynq?UltraScale+?MPSoC USB 3.0控制器由兩個(gè)獨(dú)立的雙角設(shè)備(DRD)控制器組成。兩者都可以單獨(dú)配置為在任何給定時(shí)間用作主機(jī)或設(shè)備。USB 3.0 DRD控制器通過高級(jí)可

2019-01-03 09:59:50

與內(nèi)置于 TE0720 系列 Trenz Electronic SoM(采用 Zynq Z-7014S 和 Zynq Z-7020 器件)中的 FPGA 容量相比,集成到 TE0723-03M

2018-08-31 14:43:05

是怎樣實(shí)現(xiàn)對(duì)自己的配置? 這也是本文將要和大家共同討論的問題。 Zynq的啟動(dòng)流程 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對(duì)芯片的配置,也就是PS和PL的配置是通過 PS 處理器

2021-01-08 16:33:01

本文主要與大家分享了Zynq在非JTAG模式下的啟動(dòng)配置流程,旨在讓大家對(duì)Zynq的三階段啟動(dòng)模式有一個(gè)具體的認(rèn)識(shí),希望大家多多交流。

2021-03-17 07:36:30

為了確保正確回退到金啟動(dòng),AR#67221規(guī)定QSPI閃存的D2和D3數(shù)據(jù)條應(yīng)連接到4K7上拉。但是看看Zynq xc7z030fbg676,這些引腳也可用作配置模式引腳。QSPI D2 =模式引腳

2020-06-09 17:24:31

各位i大神,小弟最近遇到了zynq上無法啟動(dòng)linux的問題,不知道哪里的錯(cuò)誤都是按照xilinx官網(wǎng)做的。。thanks

2014-07-07 12:40:30

你好我想制作一個(gè)具有中斷信號(hào)的自定義IP。我正在尋找這個(gè)中斷信號(hào)的規(guī)格。我在哪里可以找到這個(gè)規(guī)格?例如水平或邊緣檢測(cè)器如果它是水平檢測(cè)器,它應(yīng)該停留多長(zhǎng)時(shí)間?我正在使用ZYNQ ZC706板。如果你

2019-04-10 11:49:23

zynq是xilinx的新一代的嵌入ARM硬核的SOC,請(qǐng)問1、這種FPGA器件相對(duì)以往傳統(tǒng)FPGA有哪些優(yōu)勢(shì)和劣勢(shì)?2、針對(duì)圖像和視頻處理的,這兩類哪一種器件更適合?3、相同價(jià)格的情況下,ARM硬核的引入相比傳統(tǒng)FPGA是否會(huì)降低zynq的性價(jià)比和靈活度?

2022-11-07 15:28:45

Zynq-7000 AP SoC ZC706 XC7Z045 Zynq?-7000 FPGA + MCU/MPU SoC 評(píng)估板

2024-03-14 20:42:29

Xilinx-ZYNQ7000系列-學(xué)習(xí)筆記(3):系統(tǒng)復(fù)位與啟動(dòng)一、復(fù)位ZYNQ-7000 SoC系統(tǒng)中的復(fù)位可以由硬件、看門狗定時(shí)器、JTAG控制器或軟件產(chǎn)生,可用于驅(qū)動(dòng)系統(tǒng)中每個(gè)模塊的復(fù)位信號(hào)

2022-01-25 07:05:36

大家好,我正在與SoC邁出第一步,我目前正在使用Zybo Zynq開發(fā)板。我有一個(gè)簡(jiǎn)單的問題:是否可以創(chuàng)建多個(gè)設(shè)備配置,為每個(gè)配置生成比特流并將比特流存儲(chǔ)在內(nèi)存或其他內(nèi)容中,以便創(chuàng)建一個(gè)說“配置庫(kù)

2020-05-20 10:44:19

因?yàn)樽罱玫?b class="flag-6" style="color: red">zynq芯片,我希望能在zynq芯片上使用freeRTOS,但是弄不明白怎么移植進(jìn)去。一般xillinx sdk在工程里面添加操作系統(tǒng)的方法是,在repository里先安裝相應(yīng)的庫(kù)

2020-06-11 04:35:29

大家好,我使用zynq 7020開發(fā)板,其自定義架構(gòu)不支持SD卡,但支持QSPI閃存。我通過在SDK中使用以下bif文件創(chuàng)建zynq啟動(dòng)映像來構(gòu)建.msc文件 [bootloader] zynq

2020-07-30 16:24:39

Zynq-7000 Extensible Processing Platform,是一個(gè)可擴(kuò)展處理平臺(tái),簡(jiǎn)單說就是有個(gè)FPGA做外設(shè)的A9雙核處理器。所以,它的啟動(dòng)流程自然也和FPGA完全不同,而與

2015-07-22 20:42:50

做一遍也不害怕!Zynq7000,是一個(gè)可擴(kuò)展處理平臺(tái),簡(jiǎn)單說就是有個(gè)FPGA做外設(shè)的A9雙核處理器。所以,它的啟動(dòng)流程自然也和FPGA完全不同,而與傳統(tǒng)的ARM處理器類似。Zynq7000支持從多種設(shè)備

2015-05-27 20:50:06

使用source命令執(zhí)行petalinux的環(huán)境配置腳本settings.sh,如下所示:source /home/zynq/petalinux/v2018.3/settings.sh圖 31.1.2 運(yùn)行

2020-09-15 15:24:44

Xilinx官方ZYNQ EVK開發(fā)板對(duì)應(yīng)的Linux內(nèi)核,發(fā)現(xiàn)其不可以在正點(diǎn)原子的ZYNQ開發(fā)板上啟動(dòng),所以本節(jié)我們就參考Xilinx EVK開發(fā)板的設(shè)置,修改相應(yīng)的配置使其在正點(diǎn)原子的領(lǐng)航者開發(fā)板上能啟動(dòng)

2020-09-14 15:42:54

1、ZYNQ調(diào)試時(shí)內(nèi)存讀寫的一般方法假設(shè)查看的數(shù)據(jù)從地址0x0開始,大小為4個(gè)字節(jié)。打開示例工程并啟動(dòng)調(diào)試。在菜單欄選擇Window->Show View->Memory打開內(nèi)存視圖。原作者: 嵌入式男單第九名 劉廣信

2022-07-05 15:30:17

嗨,PCIe-Spec定義在穩(wěn)定供電后100ms,PCIe設(shè)備必須為鏈路訓(xùn)練做好準(zhǔn)備。使用7系列Zynq設(shè)備無法達(dá)到此時(shí)間。我使用了兩種方法來減少啟動(dòng)時(shí)間: - 優(yōu)化FSBL以達(dá)到SPI控制器的最大

2020-06-09 16:42:15

大家好,有沒有一種簡(jiǎn)單的方法可以使用IMPACT(ISE)將比特流下載到Zynq設(shè)備中而無需啟動(dòng)ARM?我知道這可以用Vivado完成。TIA

2020-07-21 15:11:31

[/td][td]關(guān)于zynq啟動(dòng)的問題,求達(dá)人解答![img][/img]查閱了些資料,發(fā)現(xiàn)zynq是分部啟動(dòng)的。1)其中arm部分是否可以軟重啟,自己收到復(fù)位命令后進(jìn)行從新加載PS部分;2)有

2013-08-23 10:49:00

如何使用Windows在Zynq 7000主板上啟動(dòng)linux?在Linux中我有終端可以請(qǐng)你建議是否有任何Windows終端以上來自于谷歌翻譯以下為原文How can I boot linux

2019-04-09 13:12:21

`玩轉(zhuǎn)Zynq連載1——Zynq的linux啟動(dòng)過程更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1概述 簡(jiǎn)單的,以u(píng)g585中的一張圖來看,從大的方面說

2019-04-16 06:56:32

`玩轉(zhuǎn)Zynq連載22——[ex03] 基于Zynq PL的PLL配置實(shí)例更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-09-06 08:13:18

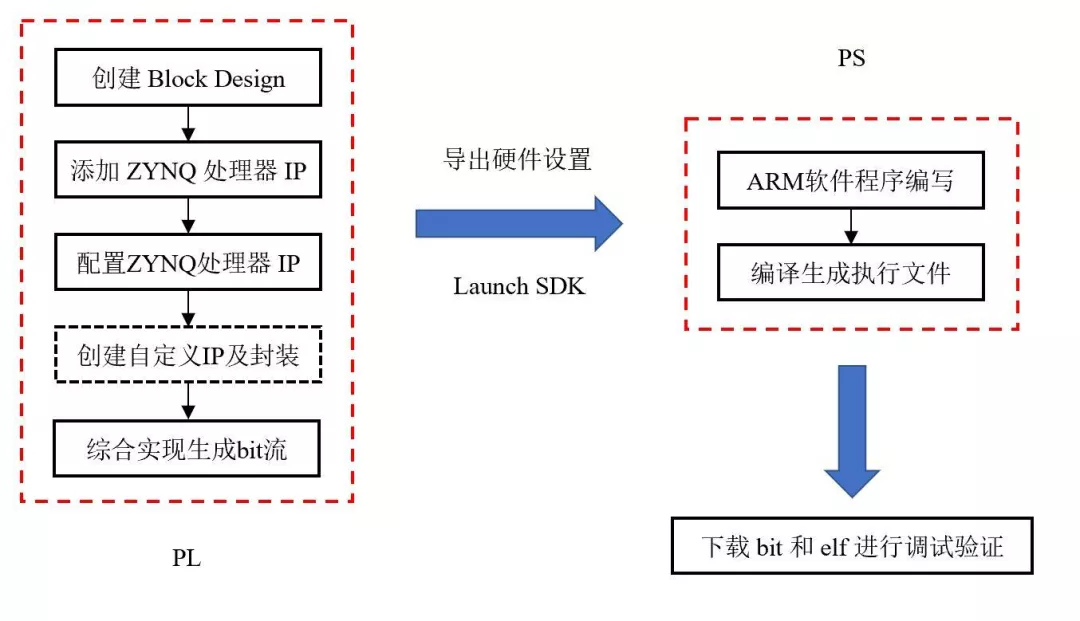

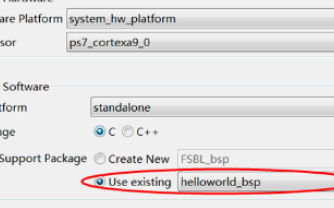

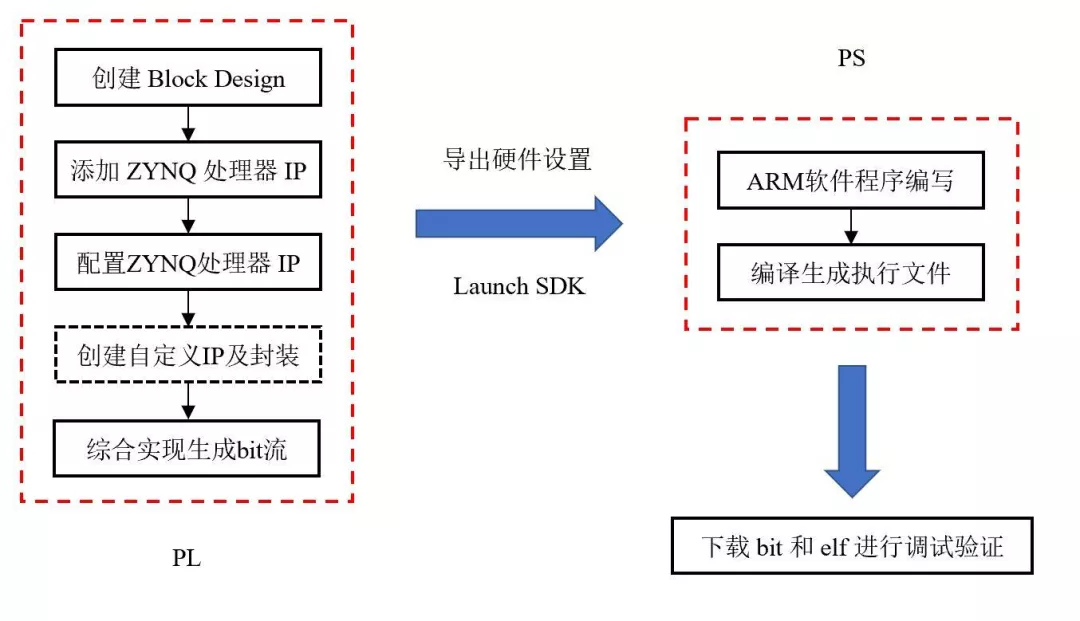

Zynq,而是如何新建Zynq系統(tǒng)模塊、配置PS的參數(shù)、導(dǎo)出硬件、新建軟件工程并且在線板級(jí)運(yùn)行起來。流程很重要,大家在開始的時(shí)候總要先走一遍流程了解開發(fā)的全貌,然后再細(xì)細(xì)把玩,逐個(gè)精通。 2 新建

2019-09-30 12:57:32

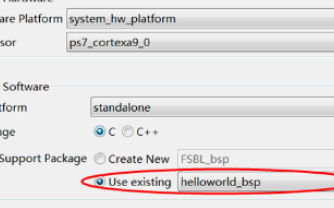

Zynq的啟動(dòng)原理,建議參考文檔《玩轉(zhuǎn)Zynq-基礎(chǔ)篇:Zynq的啟動(dòng)過程.pdf》。 2 導(dǎo)出硬件信息并啟動(dòng)SDK參考文檔《玩轉(zhuǎn)Zynq-工具篇:導(dǎo)出PS硬件配置和新建SDK工程》。 3 創(chuàng)建FSBL工程

2019-09-30 14:11:59

喜如何用zqq的irq no 52到MIO26(gpio中斷)引腳配置中斷線?我正在使用以下devicetree配置i2c1:i2c @ e0005000 {compatible =“cdns

2020-04-24 09:43:51

我正在使用zynq芯片和VIRTEX-7設(shè)計(jì)電路板。我想知道在Zynq PL引腳和Virtex-7 IO引腳之間選擇配置數(shù)據(jù)線(例如Slave SelectMAP X8,X16,X32)的方法。在

2020-06-05 10:31:19

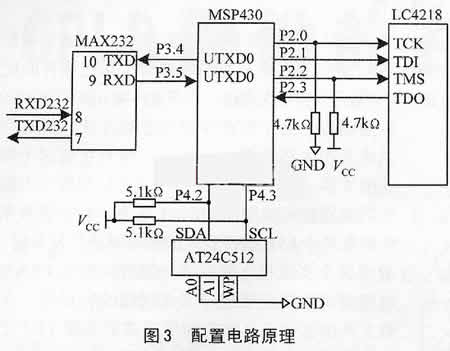

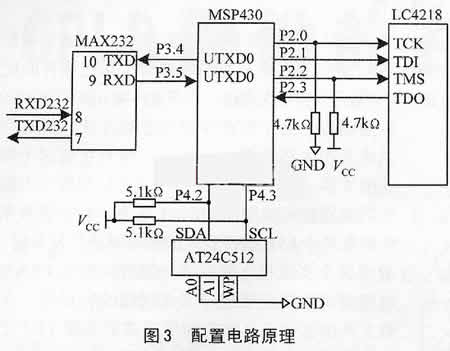

摘要:介紹基于SRAM LUT結(jié)構(gòu)的FPGA器件的上電配置方式;著重介紹采用計(jì)算機(jī)串口下載配置數(shù)據(jù)的方法和AT89C2051單片機(jī)、串行EEPROM組成的串行配置系統(tǒng)的設(shè)計(jì)方法及實(shí)現(xiàn)

2006-03-13 19:36:49 448

448 以下是引用片段: 摘要: 介紹一種利用微控制器動(dòng)態(tài)配置CPLD器件的方法。將配置文件存放在存儲(chǔ)器中,配置文件中的控制代碼驅(qū)動(dòng)在微處理器中運(yùn)行的配置引擎;將配置文件中的配置信息通過JTAG口移入

2009-06-20 10:44:21 3034

3034

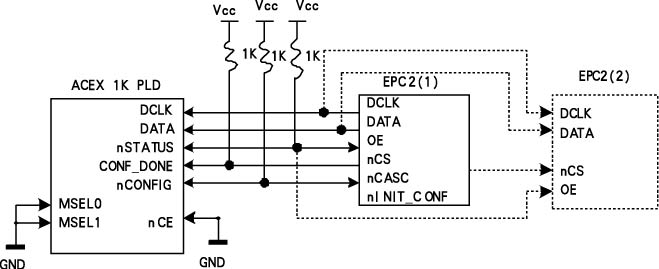

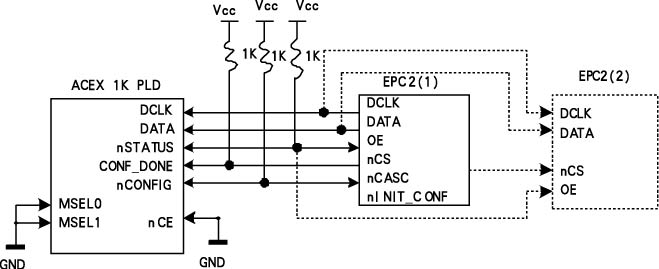

摘 要 :介紹ACEX 1K系列器件的配置方法,對(duì)幾種方法進(jìn)行了分析對(duì)比,并著重論述了應(yīng)用配置器件配置 ACEX 1K系列器件的優(yōu)點(diǎn)。

關(guān)鍵詞 :CPL

2009-06-20 10:51:54 478

478

摘要: 介紹基于SRAM LUT結(jié)構(gòu)的FPGA器件的上電配置方式;著重介紹采用計(jì)算機(jī)串口下載配置數(shù)據(jù)的方法和AT89C2051單片機(jī)、串行EEPROM組成的串行配置系統(tǒng)的設(shè)計(jì)方法及

2009-06-20 10:57:26 1062

1062

Realview MDK不僅提供了默認(rèn)的啟動(dòng)代碼,而且這些啟動(dòng)代碼可以通過圖形化界面配置。啟動(dòng)代碼的圖形化配置界面非常類似于Web網(wǎng)頁的界面,甚至后臺(tái)處理的腳本也與Html語言十分接近。下面將詳細(xì)的解析圖形化界面的設(shè)計(jì)與配置。 啟動(dòng)代碼的配置界面是由程序中的

2011-02-24 16:06:53 86

86 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 網(wǎng)絡(luò)資料收集,關(guān)于啟動(dòng)流程的一些注意點(diǎn),關(guān)于開發(fā)板ZYNQ系列的包括MIZ702

2016-05-11 17:30:15 3

3 基于單片機(jī)的復(fù)雜可編程邏輯器件快速配置方法

2017-01-18 20:35:09 8

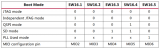

8 今天,賽靈思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎來一個(gè)新的產(chǎn)品系列及三款最新器件! 新的產(chǎn)品系列被稱為Zynq Z-7000S系列,三款新器件分別為

2017-02-08 04:25:13 517

517

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC啟動(dòng) 熊貓君在這里討論啟動(dòng)(Boot),主要是想聊它的啟動(dòng)設(shè)備和啟動(dòng)方式。看看啟動(dòng)設(shè)備是否廣泛支持,啟動(dòng)

2017-02-08 08:31:11 358

358

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC啟動(dòng) 熊貓君在這里討論啟動(dòng)(Boot),主要是想聊它的啟動(dòng)設(shè)備和啟動(dòng)方式。看看啟動(dòng)設(shè)備是否廣泛支持,啟動(dòng)

2017-02-08 08:31:11 339

339

在《ZYNQ-7000使用總結(jié)(3)——PS和PL部分配合使用》中,我們已經(jīng)可以將PL與PS部分一起使用,并且通過JTAG下載到板子運(yùn)行。對(duì)于ZYNQ,有多種啟動(dòng)方式,比如從JTAG啟動(dòng)、從QSPI

2019-10-06 16:48:00 2095

2095

在電子系統(tǒng)設(shè)計(jì)中,無任是用CPU作為系統(tǒng)的主要器件,還是用FPGA作為系統(tǒng)的主要器件,系統(tǒng)設(shè)計(jì)中首先要考慮到的問題就是處理器的啟動(dòng)加載問題。

2018-07-12 08:27:00 9919

9919

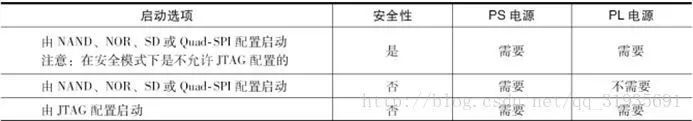

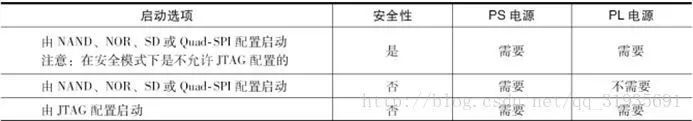

ZYNQ 7系列所有可編程器件均可以在安全模式下通過靜態(tài)存儲(chǔ)器配置或者在非安全模式下通過JTAG或者靜態(tài)存儲(chǔ)器配置。 (1)JTAG模式主要用于開發(fā)和調(diào)試 (2)NAND、并行NOR、串行NOR

2017-11-17 10:25:52 22027

22027

ZYNQ7000與傳統(tǒng)FPGA有著巨大的差異,它將自己定位為一款A(yù)ll Programmable Soc(軟硬件可編程片上系統(tǒng)),視其為以FPGA作為外設(shè)的雙核ARM A9處理器更加準(zhǔn)切。它的啟動(dòng)

2017-11-17 16:04:37 7989

7989 Zynq系列器件。如果是Mircroblaze器件請(qǐng)忽略。產(chǎn)生的“.BIN”啟動(dòng)文件可以利用(PROM programmer)拷貝到Flash或直接拷貝到SD第一個(gè)FAT分區(qū)。

2017-11-21 11:41:15 968

968 基于Zynq器件的嵌入式開發(fā)時(shí),我們不可避免地需要規(guī)劃設(shè)計(jì)使用什么樣類型和多大地內(nèi)存與FLASH,本文就ZYNQ器件的存儲(chǔ)控制器作一個(gè)拋磚引玉的描述,以期大家對(duì)它有個(gè)基本了解,如有不當(dāng)或需要補(bǔ)充之處

2017-11-22 08:23:54 6195

6195

Zynq?-7000 All Programmable SoC在單個(gè)器件上實(shí)現(xiàn)了ARM處理功能與FPGA邏輯獨(dú)特的組合,因此需要雙重的配置過程,同時(shí)需要考慮處理器系統(tǒng)和可編程邏輯。工程師會(huì)發(fā)

2018-01-12 11:17:15 5494

5494 本文試圖搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492 ZYNQ-7000如何生成從Flash和SD卡啟動(dòng)的鏡像文件 將PL與PS部分一起使用,并且通過JTAG下載到板子運(yùn)行。對(duì)于ZYNQ,有多種啟動(dòng)方式,比如從JTAG啟動(dòng)、從QSPI(即Flash

2018-05-28 11:42:14 5883

5883

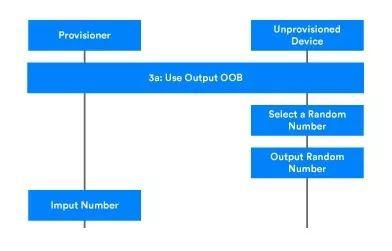

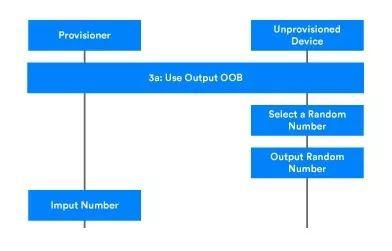

1、發(fā)送Beacon信號(hào):如果未經(jīng)啟動(dòng)配置的設(shè)備支持PB-ADV承載層,則其作為未經(jīng)啟動(dòng)配置設(shè)備Beacon進(jìn)行廣播;如果使用的是PB-GATT承載層,則發(fā)送可連接的廣播數(shù)據(jù)包。這就向啟動(dòng)配置設(shè)備(Provisioner)表明未經(jīng)啟動(dòng)配置的設(shè)備已做好準(zhǔn)備,可進(jìn)入啟動(dòng)配置流程。

2018-09-28 08:22:00 5578

5578

在本視頻中,我們將學(xué)習(xí)如何使用Xilinx SDK啟動(dòng)電路板,利用每個(gè)驅(qū)動(dòng)程序提供的應(yīng)用示例并測(cè)試各種外設(shè)。

我們將詳細(xì)介紹Zynq DRAM測(cè)試,并了解如何利用它進(jìn)行測(cè)試。

2018-11-29 06:50:00 4666

4666 了解如何配置和練習(xí)U-Boot的USB主機(jī)功能。

這允許在Zynq上使用USB記憶棒進(jìn)行數(shù)據(jù)存儲(chǔ)和檢索,包括二次啟動(dòng)。

2018-11-29 06:38:00 2554

2554 了解設(shè)計(jì)人員在使用Zynq-7000 All Programmable SoC器件時(shí)可用的不同I / O,從標(biāo)準(zhǔn)I / O到串行收發(fā)器以及模擬輸入。

2018-11-26 06:36:00 2547

2547 了解Xilinx FSBL如何操作以啟動(dòng)Zynq器件。

包括程序執(zhí)行概述,調(diào)試技巧以及有關(guān)特定引導(dǎo)設(shè)備的信息。

還包括FSBL角度的啟動(dòng)安全性簡(jiǎn)要概述。

2018-11-23 06:32:00 4237

4237 ZYNQ-7000如何生成從Flash和SD卡啟動(dòng)的鏡像文件 將PL與PS部分一起使用,并且通過JTAG下載到板子運(yùn)行。對(duì)于ZYNQ,有多種啟動(dòng)方式

2018-12-01 08:38:18 7278

7278

在ps的控制下,可以實(shí)現(xiàn)安全或非安全的配置所有ps和pl。通過zynq提供的JTAG接口,用戶可以在外部主機(jī)的控制下對(duì)zynq進(jìn)行配置,zynq不支持最開始就配置pl的過程。

2019-05-15 11:41:31 7190

7190

本文主要介紹zynq啟動(dòng)過程,主要包括BootROM和FSBL等的執(zhí)行過程。

2019-10-27 10:47:16 6952

6952

ZYNQ是一個(gè)可擴(kuò)展平臺(tái),就是有FPGA作為外設(shè)的A9雙核處理器,它的啟動(dòng)流程與FPGA完全不同,而與傳統(tǒng)的ARM處理器類似,ZYNQ的啟動(dòng)配置需要多個(gè)處理步驟。

2020-12-05 10:48:58 5388

5388 Xilinx 用兩個(gè) 96 位獨(dú)特器件標(biāo)識(shí)符(稱為器件 DNA)為每個(gè) Zynq UltraScale+ 器件編程。一個(gè) DNA 值位于可編程邏輯 (PL) 中,另一個(gè) DNA 值位于處理系統(tǒng) (PS) 中。這兩個(gè) DNA 值是不同的,但每個(gè) DNA 都有以下屬性及讀取訪問方法。

2022-02-08 14:19:49 1149

1149

初學(xué) Zynq 的時(shí)候,都是按照慣例打開 Vivado 軟件,然后實(shí)現(xiàn) Zynq 可編程邏輯硬件部分PL的設(shè)置后,把硬件部署導(dǎo)出,再打開 SDK 進(jìn)行 ARM 核的軟件部分 PS 編程設(shè)計(jì),最后再將

2022-02-08 11:48:37 1021

1021

初學(xué) Zynq 的時(shí)候,都是按照慣例打開 Vivado 軟件,然后實(shí)現(xiàn) Zynq 可編程邏輯硬件部分PL的設(shè)置后,把硬件部署導(dǎo)出,再打開 SDK 進(jìn)行 ARM 核的軟件部分 PS 編程設(shè)計(jì),最后再將

2021-01-26 07:30:29 20

20 。如圖2.1所示,在相對(duì)較高層次對(duì)比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復(fù)雜。本章,將介紹這三種器件的特點(diǎn)。 2.1 技術(shù)時(shí)間線 進(jìn)一步介紹之前,需要指出這三種

2021-04-02 17:20:14 13783

13783

在本篇博文中,我們將探討如何在 Vitis 中調(diào)試 Zynq UltraScale 器件啟動(dòng)鏡像。這些啟動(dòng)鏡像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中

2021-06-01 15:35:45 2709

2709

為處理海量數(shù)據(jù)、復(fù)雜算法、超低延時(shí)的應(yīng)用提供數(shù)字化加速驅(qū)動(dòng)力是賽靈思一直的目標(biāo),為此,賽靈思研發(fā) Bootgen 工具支持將二進(jìn)制文件縫合在一起并生成器件啟動(dòng)鏡像。定義了多個(gè)屬性和參數(shù)作為創(chuàng)建啟動(dòng)

2021-08-27 14:11:30 2832

2832 FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法(深圳市村田電源技術(shù)有限公司)-FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13 功耗域2.2 低功耗域2.3 全功耗域2.4 PL功耗域2.5 PMU一、電源優(yōu)化方法相對(duì)于上一代Zynq器件,Zynq UltraScale+更加...

2021-11-06 21:06:04 6

6 在 Xilinx Zynq 器件中,硬件可編程邏輯 PL 是作為一項(xiàng)外設(shè)掛載在 ARM 處理器系統(tǒng)中的,那么 PL 硬件的配置自然也就由處理器負(fù)責(zé)。本文...

2022-02-07 11:18:27 1

1 ZYNQ7000 SOC 芯片可以從 FLASH 啟動(dòng),也可以從 SD 卡里啟動(dòng), 本節(jié)介紹程序 FLASH 啟動(dòng)的方法。Zynq7000 SOC 芯片上電后,最先運(yùn)行的是ARM端系統(tǒng)(PS

2022-05-07 09:41:35 5019

5019 普通的 FPGA 一般是可以從 flash 啟動(dòng),或者被動(dòng)加載,但是ZYNQ不行,ZYNQ必須PS端參與

2022-07-22 10:10:02 5209

5209 Zynq MPSoC是Zynq-7000 SoC(之后簡(jiǎn)稱Zynq)的進(jìn)化版本。Zynq是賽靈思發(fā)布的集成PL(FPGA)和PS設(shè)計(jì)的最早的一代產(chǎn)品。如圖2.1所示,在相對(duì)較高層次對(duì)比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復(fù)雜。本章,將介紹這三種器件的特點(diǎn).

2022-08-15 09:16:38 1629

1629 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對(duì)芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實(shí)現(xiàn)的。需要注意的是,與傳統(tǒng)的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進(jìn)行直接啟動(dòng)配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 986

986 FPGA器件配置方式分三大類:主動(dòng)配置、被動(dòng)配置和JTAG配置。 主動(dòng)配置:由FPGA器件引導(dǎo)配置操作過程。 被動(dòng)配置:由計(jì)算機(jī)或控制器控制配置過程。上電后,控制器件或主控器把存儲(chǔ)在外部存儲(chǔ)器

2022-11-17 12:15:10 1141

1141 介紹一下Xilinx公司的新一代Zynq UltraScale+ RFSoC器件,可用于LTE、5G、SDR、衛(wèi)星通信等無線平臺(tái)。

2023-05-22 10:38:59 3966

3966

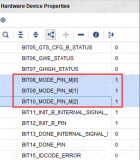

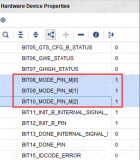

本文介紹使用Xilinx?SDK軟件查看當(dāng)前Zynq?SoC啟動(dòng)模式的步驟

2023-07-07 14:15:00 1179

1179

在 “ 什么是軟啟動(dòng)?軟啟動(dòng)時(shí)間?啟動(dòng)時(shí)間?”文章中,我們簡(jiǎn)述了為開關(guān)電源配置一個(gè)最小的軟啟動(dòng)時(shí)間,至少可以獲得兩個(gè)好處。

2023-07-23 10:35:06 1102

1102

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC中的隔離方法.pdf》資料免費(fèi)下載

2023-09-13 17:11:48 1

1 電子發(fā)燒友網(wǎng)站提供《Zynq-7000 SoC的安全啟動(dòng)應(yīng)用說明.pdf》資料免費(fèi)下載

2023-09-13 11:46:04 1

1 電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+器件封裝和管腳用戶指南.pdf》資料免費(fèi)下載

2023-09-13 10:30:45 1

1 Zynq器件將arm和FPGA結(jié)合,利用了兩者各自的優(yōu)勢(shì),arm可以實(shí)現(xiàn)靈活的控制,而FPGA部分可以實(shí)現(xiàn)算法加速,這大大擴(kuò)展了zynq的應(yīng)用。比如深度學(xué)習(xí)加速,圖像處理等等。PL側(cè)表示FPGA的邏輯部分,PS側(cè)為arm端以及一些AXI接口控制部分,二者實(shí)際上通過AXI接口實(shí)現(xiàn)通信和互聯(lián)。

2023-11-09 11:28:04 1460

1460

正在加载...

8313

8313 8313

8313

6687

6687 6687

6687

3490

3490 3490

3490

4952

4952 4952

4952

5212

5212 5212

5212 736

736 736

736

506

506 506

506

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論