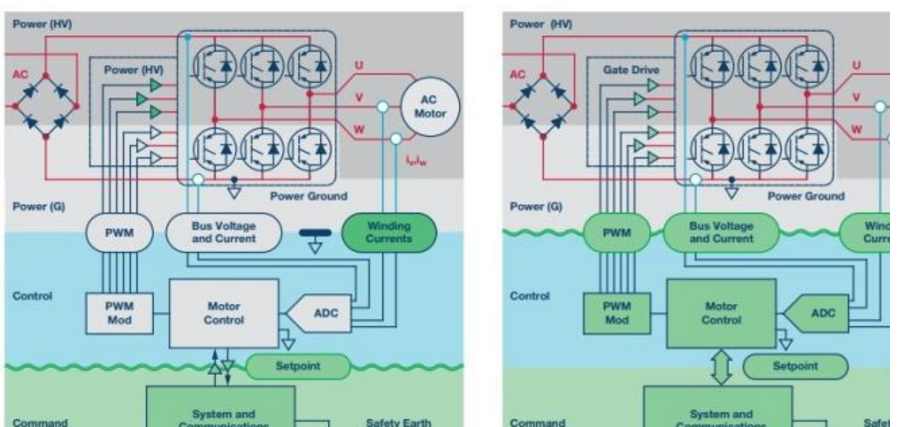

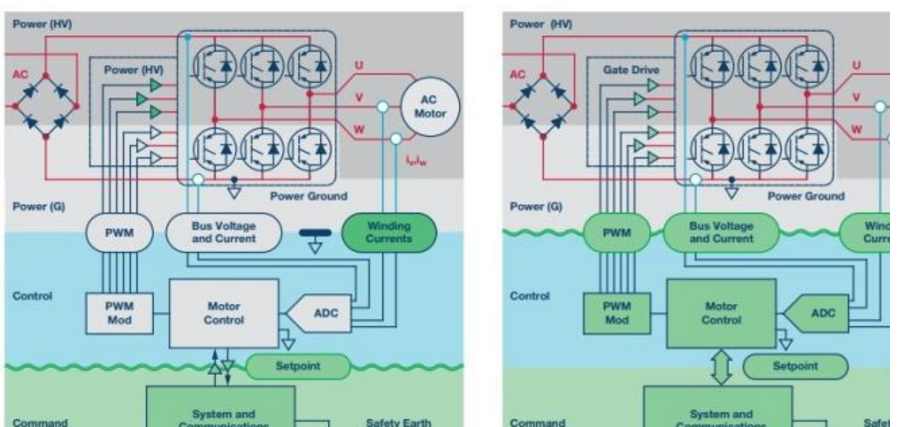

本文探討了系統(tǒng)架構(gòu)選擇對(duì)電源和控制電路設(shè)計(jì)以及系統(tǒng)性能的影響。本文還將說明最新可用隔離元件的性能提升如何幫助替代架構(gòu)在不影響安全性的前提下提升系統(tǒng)性能

2017-10-13 06:12:00 7576

7576

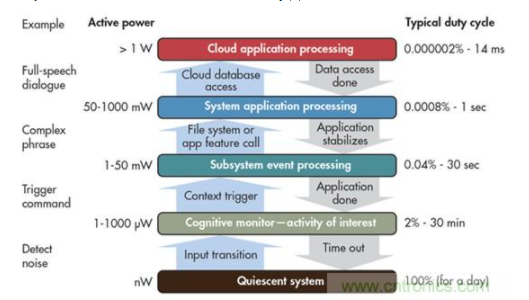

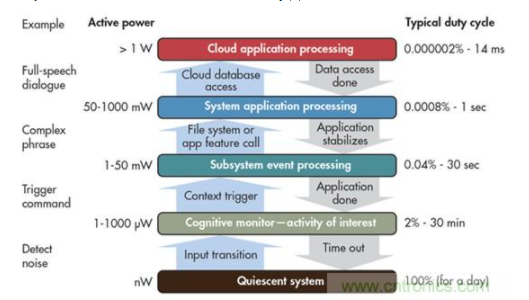

如何在繼續(xù)為客戶營(yíng)造愉悅體驗(yàn)的前提下,實(shí)現(xiàn)響應(yīng)速度、成本和功耗之間的平衡?本文中,我們將就此問題進(jìn)行探討,并介紹如何采用“認(rèn)知分層”的方法搭建Always-On架構(gòu),幫助設(shè)計(jì)師實(shí)現(xiàn)產(chǎn)品設(shè)計(jì)的最佳平衡。

2021-03-25 13:56:06 4056

4056

我確實(shí)遇到了一個(gè)我想解決的問題。這更像是Vivado的實(shí)現(xiàn)問題。我正在嘗試使用ILA內(nèi)核和探針將調(diào)試內(nèi)核添加到我的設(shè)計(jì)中。執(zhí)行設(shè)計(jì)后,我收到以下錯(cuò)誤:[Chipscope 16-119]實(shí)現(xiàn)調(diào)試核心

2019-01-03 11:00:14

嗨,我有spartan 3a評(píng)估套件,我試圖將Chipscope ILA添加到我的設(shè)計(jì)中但是我在實(shí)現(xiàn)的設(shè)計(jì)部分中收到了錯(cuò)誤。錯(cuò)誤:NgdBuild:1317- 使用核心芯片eye_ila_v1需要

2018-12-12 10:47:57

我正按照XTP039中的說明嘗試使用SP601 MIG參考設(shè)計(jì)(RDF0005)。參考設(shè)計(jì)包括可立即下載的比特流和可立即構(gòu)建的設(shè)計(jì)。當(dāng)我使用ChipScope下載預(yù)先構(gòu)建的比特流時(shí),一切都

2019-08-27 11:21:10

,都有Xilinx公司自己寫好的可綜合的模塊,想請(qǐng)教一下為什么要分成這樣兩項(xiàng)?它們里面的模塊有區(qū)別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區(qū)別呢?

2013-09-28 18:17:54

,都有Xilinx公司自己寫好的可綜合的模塊,想請(qǐng)教一下為什么要分成這樣兩項(xiàng)?它們里面的模塊有區(qū)別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區(qū)別呢?

2013-09-28 18:20:29

你好親愛的社區(qū),我在相對(duì)較新版本的ISE工具(Chipscope 14.7)中遇到了一個(gè)非常奇怪的錯(cuò)誤。每當(dāng)我嘗試以下錯(cuò)誤就出來了。我搜索了社區(qū),我找到的唯一解決方案是在Windows中取消UAC

2020-04-16 09:56:37

將設(shè)計(jì)上傳到FPGA中。但是當(dāng)我嘗試使用chipScope Pro進(jìn)行分析時(shí),它會(huì)返回一條警告,表示沒有連接Xilinx平臺(tái)的USB電纜。我使用的是Windows 10。請(qǐng)告訴我們可以做些什么。問候

2019-04-18 12:38:46

嗨,大家好。我在安裝ISE13.1并運(yùn)行完全在ISE12.1中的項(xiàng)目后遇到如下問題,我在ISE13.1中檢查了.cdc文件是否正確。那么有人可以給我一些建議嗎?加載CDC項(xiàng)目F

2018-12-12 10:41:37

問題描述:我要通過spi獲取ADC ROM中的內(nèi)容。在綜合后進(jìn)行仿真,其結(jié)果和想要的結(jié)果一致,如圖1所示。然后加入chipscope進(jìn)行數(shù)據(jù)的抓取,但出現(xiàn)如下圖的結(jié)果。其中FPGA的輸入

2018-06-04 10:34:29

我在綜合仿真中遇到一個(gè)問題,希望各位大俠能提供幫助,謝謝!問題是這樣的:該項(xiàng)目是在ise7.1i的環(huán)境下設(shè)計(jì)的,綜合可以通過,但是現(xiàn)在我們換成版本9.2i的,不能通過綜合,出現(xiàn)的錯(cuò)誤提示是:Xst

2009-09-25 11:15:23

嗨,今天我不得不使用ISE 14.7在一個(gè)舊項(xiàng)目上做一些工作,我最近一直在使用Vivado。我需要使用Chipscope但它拒絕找到我的平臺(tái)電纜,唯一的錯(cuò)誤信息是。警告:未連接Xilinx

2019-04-12 14:33:19

您好,如題,AD7656BSTZ在保證供電和輸入模擬信號(hào)不超的前提下,什么原因會(huì)導(dǎo)致芯片±15V(VDD和VSS)引腳被燒,謝謝!手冊(cè)中提到每個(gè)引腳最大的電流不能超過10mA。

2023-12-14 08:23:29

一定的時(shí)間內(nèi)得不到響應(yīng)就開始使它不斷的復(fù)位,保持喚醒狀態(tài),但這樣造成的后果是功耗非常大(正常工作狀態(tài)下工作電流大概是2ma,復(fù)位狀態(tài)下是30ma)。請(qǐng)問如何低功耗前提下還有什么辦法喚醒終端?

2016-03-22 11:52:53

ESP32串口0用于下載程序跟輸出log,現(xiàn)在我想通過串口工具發(fā)送幾個(gè)字節(jié)的數(shù)據(jù)過去,程序內(nèi)未做任何初始化,直接采用uart_read_bytes讀取發(fā)現(xiàn)在沒有發(fā)送數(shù)據(jù)時(shí)候也一直讀取到數(shù)據(jù)想不影響UART0本來原有的下載+LOG功能的前提下,在輸入口增加接收功能,有辦法實(shí)現(xiàn)么?

2023-02-20 06:28:52

本人菜鳥一枚,請(qǐng)問FPGA中(使用verilog)ChipScope顯示輸入時(shí)鐘信號(hào)(clk50M),報(bào)錯(cuò)誤,如果通過pll獲取其他頻率比如clk40M,為什么ChipScope顯示的時(shí)鐘頻率一直為

2017-05-09 20:31:19

1 功能概述該工程實(shí)例內(nèi)部系統(tǒng)功能框圖如圖所示。我們通過IP核例化一個(gè)FIFO,定時(shí)寫入數(shù)據(jù),然后再讀出所有數(shù)據(jù)。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)FIFO

2019-04-08 09:34:42

沒有被ISE集成,即便是從ISE中打開core gen,也需要重新建立core gen工程,甚至需要選擇與工程一樣的元器件,并且生成IP核之后還需要手動(dòng)添加到ISE工程內(nèi)。(為了公平測(cè)試綜合性能,本例

2021-01-08 17:07:20

嗨,我對(duì)Xilinx ISE中生成的報(bào)告有疑問。我有一個(gè)設(shè)計(jì),我正在檢查綜合和布局和路線報(bào)告。我對(duì)我的設(shè)計(jì)進(jìn)行了一些更改并實(shí)施了它。我想檢查更改的啟動(dòng)和邏輯利用率,但報(bào)告是相同的。我嘗試了很多次更改

2019-02-20 07:19:58

嗨,我們正在使用Xilinx ISE V13.4,突然間我們得到了Xilinx內(nèi)核插入錯(cuò)誤。請(qǐng)?jiān)谙旅嬲业皆敿?xì)信息,附上詳細(xì)的錯(cuò)誤報(bào)告。芯片范圍項(xiàng)目早期工作,信號(hào)添加和信號(hào)沒有變化。網(wǎng)表也沒有變化。請(qǐng)

2020-05-04 12:09:30

/1jGjAhEm 1 工程移植可以復(fù)制上一個(gè)實(shí)例sp6ex9的整個(gè)工程文件夾,更名為sp6ex10。然后在ISE中打開這個(gè)新的工程。接著將這個(gè)工程的各個(gè)功能模塊代碼輸入的相應(yīng)的設(shè)計(jì)文件中。除了

2015-11-25 13:45:30

配置如附件所示,功耗為30UA是否正常,不改變靈敏度的前提下,是否有其它方式可降低功耗

2016-08-02 18:23:12

【樹莓派小車?yán)@樁實(shí)驗(yàn)報(bào)告】電導(dǎo) 沒過樹莓 燒過小車 愛過一、實(shí)驗(yàn)?zāi)康模?b class="flag-6" style="color: red">綜合運(yùn)用本學(xué)期學(xué)習(xí)的內(nèi)容,實(shí)現(xiàn)小車完整地在“8”字形跑道上巡線行駛在保證小車不撞墻、不撞箱、不走錯(cuò)跑道的三大前提下,盡可能地跑出

2022-01-14 07:10:33

什么是ISEISE是使用XILINX的FPGA的必備的設(shè)計(jì)工具,它可以完成FPGA開發(fā)的全部流程,包括設(shè)計(jì)輸入、仿真、綜合、布局布線、生成BIT文件、配置以及在線調(diào)試等,功能非常強(qiáng)大。ISE除了我們

2009-11-23 16:13:52

文本編輯器打開的文本文件。Xilinx自家的綜合結(jié)果是NGC網(wǎng)表。NGC網(wǎng)表是二進(jìn)制的文件,不能用文本編輯器打開觀察。3. 綜合網(wǎng)表中包含一些什么內(nèi)容?綜合網(wǎng)表中除了包含從HDL語言中infer出的與門

2018-08-08 10:31:27

請(qǐng)有人做“使用ChipScope分析設(shè)計(jì)”我的附加項(xiàng)目與ISE并通過電子郵件發(fā)送給我整個(gè)項(xiàng)目。因?yàn)楫?dāng)我做“使用ChipScope分析設(shè)計(jì)”我的項(xiàng)目時(shí),cpj文件沒有制作,我不知道為什么!?sallysoli @ gmail.comLgoicAnalyzer1.rar 814 KB

2020-04-10 10:53:27

我在使用chipscope編譯ISE(webtpack)期間遇到以下錯(cuò)誤。 (我剛剛購買了ChipScope并安裝了許可證)。有什么想法嗎?我很欣賞這個(gè)。錯(cuò)誤:NgdBuild:1317- 使用核心

2018-11-28 15:12:01

親愛的同事,我向你致意,我希望得到你的幫助!我在Project Navigator中創(chuàng)建了vhdl項(xiàng)目,在我的項(xiàng)目中添加了新的源chipcopefile.cdc,啟動(dòng)了ChipScope 64位

2018-12-11 11:15:26

嗨,如果我們?yōu)?b class="flag-6" style="color: red">Chipscope購買許可證,我們可以在ISE webPACK中使用它(我們需要維護(hù)我們的舊設(shè)計(jì))和Vivado webPACK嗎?以上來自于谷歌翻譯以下為原文Hi, if we

2018-12-14 11:30:42

我想問下在can底層驅(qū)動(dòng)配置好的前提下,我向DSP發(fā)送任何數(shù)據(jù),can就能接收到數(shù)據(jù)嗎,然后將RMP=1即ECanaShadow.CANRMP.bit.RMP1 = 1;還是說必須發(fā)送的數(shù)據(jù)符合一定的格式,can郵箱才能將RMP=1.我現(xiàn)在想問的是如何觸發(fā)can的接收郵箱,讓接收郵箱的的RMP=1.

2020-07-08 15:39:18

本帖最后由 eehome 于 2013-1-5 09:49 編輯

在不影響選擇原有器件前提下,在KEIL下增加STC單片機(jī)針對(duì)KEIL UV4 有效1、在 X:\Keil\c51\inc\ 解壓以下附件 2、在 X:\Keil\uv4\ 解壓以下附件即可 結(jié)果如下圖所示:

2011-05-10 15:18:14

如何在ISE環(huán)境中使用ModelSim仿真

2012-08-20 18:45:23

RX of未使用的QUAD連接到GND,但是一些參考板使它們保持打開狀態(tài)。哪個(gè)更合理?您是否會(huì)簡(jiǎn)要說明如何在未使用的QUAD和部分使用的QUAD中連接RX,TX,MGTREFCLK?例如,QUAD115和QUAD112?

2020-06-17 08:00:12

如何在IAR中實(shí)現(xiàn)printf函數(shù)功能?

2021-12-01 06:29:17

組成,在內(nèi)核代碼完全開放的前提下,不同領(lǐng)域和不同層次的用戶可以根據(jù)自己的應(yīng)用需要很容易地對(duì)內(nèi)核進(jìn)行改造,在低成本的前提下,設(shè)計(jì)和開發(fā)出真正滿足自己需要的嵌入式系統(tǒng)。隨著電子市場(chǎng)的發(fā)展壯大,高性能低功耗

2019-07-17 08:11:03

我做了ISE的Web客戶端安裝它無法安裝驅(qū)動(dòng)程序。是否有文檔告訴我如何在Linux上開始使用ISE?安裝完成后,我看到了文件夾:/opt/Xilinx/11.1但是為了啟動(dòng)ISE,我需要

2018-11-19 14:36:00

the terminal by typing in ise and impact. I could not figure out the command to invoke chipscope pro and EDK.

2019-03-28 14:26:03

網(wǎng)卡的Uboot,在不更換Uboot的前提下,需要下什么命名打開這個(gè)網(wǎng)卡,解決掉這個(gè)錯(cuò)誤呢?Thanks!OpenJTAG> ping 192.168.0.102ERROR: resetting DM9000

2019-09-25 22:14:01

在FPGA中,動(dòng)態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對(duì)時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。那么該如何在低端FPGA中實(shí)現(xiàn)DPA的功能呢?

2021-04-08 06:47:08

今天教大家如何在電腦上不影響QQ正常使用的前提下,禁止訪問QQ空間。IE的那個(gè)設(shè)置不行,因?yàn)橐坏┑卿泀zone.qq.com網(wǎng)站,qq程序會(huì)自動(dòng)引導(dǎo)解除屏蔽,改hosts也不行,所以我們要用其他

2013-04-28 15:02:31

我是7系列FPGA的新手。最近開始使用Xilinx VC707板。在此之前,我曾經(jīng)在Virtex 5上工作。我有一個(gè)ISE項(xiàng)目,使用Xilinx ISE和Chipscope使用Vitex 5板進(jìn)行

2020-07-28 10:18:04

本帖最后由 eehome 于 2013-1-5 10:00 編輯

我是分別寫了兩個(gè)程序,然后怎樣使這兩個(gè)程序在一個(gè)工程里分別調(diào)用,怎樣寫一個(gè)程序調(diào)用不同的文件???我現(xiàn)在分別寫好了時(shí)鐘和日期兩個(gè)程序,在不變化這兩個(gè)程序的前提下如何用按鍵實(shí)現(xiàn)兩個(gè)功能的切換。

2012-08-10 19:40:24

如何簡(jiǎn)單檢測(cè)段式LCD的分壓方式,在沒有LCD資料的前提下。謝謝有知道的告訴下

2014-01-14 17:08:43

嗨,我是ZYNQ-7 ZC702評(píng)估板的新手,并按照ZYNQ 7000教程來習(xí)慣它。但是我在第4章(使用SDK和ChipScope調(diào)試)中遇到了麻煩,無法弄清楚問題是什么以及如何解決它......在

2019-11-08 15:21:30

我們購買了ChipScope pro版本9.2i +串行IO工具套件(2008年底)。有沒有辦法獲得使用當(dāng)前ISE13.2的許可證,還是需要購買使用此版本ISE的新版ChipScope?如果是:我該

2018-11-22 11:45:04

在不使用外界信號(hào)的前提下,使用軟件自身的數(shù)據(jù)庫能否仿真出心電信號(hào),如果可以,怎樣仿真?

2016-08-30 17:07:28

你好,當(dāng)我在Windows中雙擊Analyzer圖標(biāo)時(shí),Windows 10工具欄中會(huì)出現(xiàn)一個(gè)非常短暫的小圖標(biāo)(幾分之一秒),然后消失。沒有其他對(duì)話框或消息出現(xiàn),并且Chipscope無法啟動(dòng)

2020-05-25 07:30:04

嗨,由于未連接的Chipscope信號(hào),我在PlanAhead 14.7中收到以下錯(cuò)誤:錯(cuò)誤:[Chipscope 16-30]調(diào)試端口'cs_ila_0 / DATA'上有5個(gè)未連接的通道。這可

2018-10-19 14:36:55

在10.1中打開此外,是否可以在11.1中打開11.5 ISE項(xiàng)目?總是感謝幫助。謝謝,祖賓以上來自于谷歌翻譯以下為原文Simple question - Can I have Xilinx ISE

2018-11-21 14:32:33

安裝ISE10.1完成后,新建文件時(shí)出現(xiàn)如圖所示的選擇框,沒有chipScope文件格式,求大神指點(diǎn)

2013-09-22 09:42:38

labview建立了運(yùn)行時(shí)菜單,包含用戶登錄和退出,求教大神們,在不退出軟件的前提下,怎么實(shí)現(xiàn)用戶的退出和再登入?

2018-05-03 15:46:33

不改變IDF環(huán)境的前提下,如何設(shè)置成32M?2. menuconfig打開 Support for external, SPI-connected RAM 選項(xiàng)后,通過gc.mem_free()得到的數(shù)值是3663856,也就是只有3M多點(diǎn),哪里的問題?

2023-03-06 06:40:27

不改變IDF環(huán)境的前提下,如何設(shè)置成32M?2. menuconfig打開 Support for external, SPI-connected RAM 選項(xiàng)后,通過gc.mem_free()得到的數(shù)值是3663856,也就是只有3M多點(diǎn),哪里的問題?

2023-02-13 06:59:31

我有個(gè)觸摸按鍵開關(guān)的燒水器,現(xiàn)在想用單片機(jī)實(shí)現(xiàn)物聯(lián)網(wǎng)控制開關(guān),接上單片機(jī)后,拉高引腳,可以實(shí)現(xiàn)觸摸按鍵的操控了,但是手指觸控這個(gè)觸摸按鍵時(shí),卻不是很靈敏了。所以想請(qǐng)教一下,1 影響觸摸按鍵靈敏度的因素有什么2 怎么能單片機(jī)的引腳不影響觸摸靈敏度

2021-03-21 22:08:37

請(qǐng)問MIMO為什么能在不增加帶寬的前提下成倍的提高信道容量呢?

2023-05-16 16:35:25

我有一個(gè)ISE 14.7的完整注冊(cè)安裝。我試圖第一次使用Chipscope,它說我沒有正確的許可證。如果我有完整的ISE14.7,是否需要單獨(dú)的Chipscope許可證?我必須購買或者我可以評(píng)價(jià)一段時(shí)間嗎?

2020-04-26 06:46:54

請(qǐng)各位前輩們幫忙,小弟遇到了問題解決不了下圖所示,通上電源后,在沒有給PWM信號(hào)的前提下,風(fēng)扇自動(dòng)運(yùn)轉(zhuǎn)起來了,請(qǐng)問各位大神是什么原因造成的有此現(xiàn)象,怎樣解決。

2017-04-26 19:07:22

鍵盤掃描程序,xilinx提供,設(shè)計(jì)文件用ISE打開 設(shè)計(jì)文件

Project Navigator Auto-Make Log File

2009-06-14 09:26:28 37

37 在介紹車載綜合系統(tǒng)需求的前提下,研究和設(shè)計(jì)一種基于嵌入式S3C2410芯片的車載綜合系統(tǒng)的主板,該主板以32位微處理器和ZigBee中控門禁系統(tǒng)、GPRS、GPS、車況診斷系統(tǒng)、人機(jī)界面等

2010-07-13 17:43:00 14

14 本教程假定用戶已有安裝好仿真、綜合、ISE 和相應(yīng)的Chipscope,教程使用的環(huán)境如 下: 仿真:Modelsim 5.8 綜合:Synplify pro 7.5.1 布局:ISE 6.2 分析:Chipscope 6.2

2011-05-10 14:49:52 0

0 大功率LED用于照明是本世紀(jì)的新課題,其節(jié)能、安全、使用壽命長(zhǎng)的綜合優(yōu)點(diǎn)將引發(fā)新一輪照明革命。在需要用電池供電的 LED手電筒 應(yīng)用中,如何在使用相同電池的前提下,延長(zhǎng)電池

2011-08-24 16:46:32 102

102 Xilinx chipscope使用方法,針對(duì)剛剛開始接觸FPGA的同學(xué),零基礎(chǔ)學(xué)習(xí)。

2016-03-21 16:57:04 1

1 華清遠(yuǎn)見FPGA代碼-ChipScope功能演示

2016-10-27 18:07:54 4

4 1、代碼輸入(1)、新建一個(gè)ISE工程,名字為count4。(2)、新建一個(gè)verilog文件

2017-02-10 15:48:09 5067

5067

在ISE中打開以前做的一個(gè)工程時(shí),總是不停地提示 INFO:sim:760 - You can use the CORE Generator IP upgrade flow to upgrade

2017-02-11 10:58:52 3943

3943

然后可以打開下載電纜和開發(fā)板的電源了。接下來在ISE Project Navigator的工程文件夾視圖中點(diǎn)擊“Analyze Design Using ChipScope”,ISE即可自動(dòng)完成翻譯

2017-02-11 12:31:19 1262

1262 本文介紹了ise中chipscope的使用

2017-09-15 17:38:51 8

8 軍用機(jī)器人趨勢(shì)不可逆,如何在不阻礙技術(shù)進(jìn)步的前提下進(jìn)行監(jiān)管,這是需人類共同解決的問題。

2017-12-05 10:50:55 4235

4235 智慧醫(yī)療的真正實(shí)現(xiàn)要在萬物互聯(lián)的前提下 ,數(shù)據(jù)共享是其中非常關(guān)鍵的環(huán)節(jié)。“現(xiàn)在醫(yī)院基本上都只是開放手術(shù),而不愿開放數(shù)據(jù)。”

2019-04-18 14:29:55 1738

1738 5G網(wǎng)絡(luò)技術(shù)具有大帶寬、高速率、低時(shí)延的特點(diǎn),突破了4G的壁壘,使圖像、音頻的傳輸再也不用擔(dān)心卡頓的問題,這為未來智慧醫(yī)療的實(shí)現(xiàn)帶來了可能。

2019-06-21 09:44:38 1281

1281 運(yùn)營(yíng)商大數(shù)據(jù)精準(zhǔn)營(yíng)銷系統(tǒng)是在確保用戶隱私安全的前提下,用基于運(yùn)營(yíng)商的海量真實(shí)數(shù)據(jù)進(jìn)行深度分析,整合多種渠道,為企業(yè)提供全方位觸達(dá)客戶的營(yíng)銷方式,相比傳統(tǒng)營(yíng)銷的優(yōu)勢(shì)有:數(shù)據(jù)更精準(zhǔn),方式更靈活,優(yōu)化可見等。

2019-08-02 08:41:51 3291

3291 功能時(shí)感應(yīng)有人的前提下,電燈自動(dòng)打開。然后主人外出將自動(dòng)關(guān)閉,這樣就能達(dá)到智能省電,對(duì)于馬大哈的福利。

2020-06-01 14:39:53 936

936 當(dāng)測(cè)溫成為商業(yè)綜合體每天必須面對(duì)的大工程,如何在避免接觸的前提下高效地完成體溫檢測(cè)?在廣州,高新興5G防疫機(jī)器人承擔(dān)起這項(xiàng)任務(wù)。

2020-08-24 11:46:24 1841

1841 流的問題方面有所突破,能做到在有巨量觀眾的前提下無延時(shí)直播。這讓他對(duì)搜狐視頻的未來充滿信心。他表示,“不擔(dān)心短視頻紅海,堅(jiān)信最好的作品來自用戶。”

2020-09-16 11:51:59 2084

2084 作為亞洲規(guī)模較大的通信展,通信行業(yè)的風(fēng)向標(biāo),2020年中國(guó)國(guó)際信息通信展16日正式落下帷幕。今年正值5G商用一周年,在5G已形成規(guī)模部署的前提下,5G應(yīng)用如何落地成為本屆通信展的焦點(diǎn)。

2020-10-19 11:48:18 2072

2072 用戶提問:看了這么多個(gè)數(shù)據(jù)可視化工具的介紹,似乎都需要有網(wǎng)絡(luò)支持,但我們公司需要在不連外網(wǎng)的前提下做數(shù)據(jù)可視化分析,那怎么辦?還能用數(shù)據(jù)可視化工具嗎?

2021-10-09 10:58:15 229

229 一般情況下ILA和VIO都是用在chipscope上使用,VIO可以作為在chipscope時(shí)模擬IO。

2022-06-12 15:51:54 1682

1682 如何在成本可控的前提下,高效地推動(dòng)城市 NOA(領(lǐng)航輔助駕駛)的量產(chǎn)?

2022-09-02 11:12:19 2280

2280 作為全球LED顯示屏生產(chǎn)制作大國(guó),中國(guó)LED顯示屏行業(yè)發(fā)展日漸完備,國(guó)內(nèi)市場(chǎng)依然龐大,經(jīng)歷國(guó)內(nèi)終端市場(chǎng)需求疲軟的局面,在國(guó)內(nèi)國(guó)際經(jīng)濟(jì)雙循環(huán)的前提下,未來LED顯示屏行業(yè)的國(guó)內(nèi)市場(chǎng)發(fā)展前景

2023-03-03 15:32:09 1309

1309 ChipScope是Xilinx提供的一個(gè)校驗(yàn)FPGA設(shè)計(jì)的工具。它的本質(zhì)是一個(gè)虛擬的邏輯分析儀,能調(diào)用FPGA內(nèi)部的邏輯資源對(duì)代碼中的各個(gè)變量進(jìn)行抓取分析。

2023-05-08 16:55:20 3792

3792

、功能性要求的前提下進(jìn)行優(yōu)化整體設(shè)計(jì),實(shí)現(xiàn)小型化、減量化,顏色與桿體顏色協(xié)調(diào)統(tǒng)一。綜合機(jī)箱應(yīng)根據(jù)設(shè)備管理需求采用分倉設(shè)計(jì),箱內(nèi)的倉位數(shù)量應(yīng)與智慧燈桿的配套設(shè)備相匹

2022-04-22 10:59:30 329

329

利亞德表示:“由于市場(chǎng)環(huán)境復(fù)雜,每個(gè)企業(yè)的經(jīng)營(yíng)方式都不一樣。”今年以來,公司采取漲價(jià)措施,一方面是在原材料價(jià)格上漲的前提下,保障了公司的總利潤(rùn)率和穩(wěn)定健康發(fā)展,同時(shí)也有助于促進(jìn)led產(chǎn)業(yè)鏈恢復(fù)正常發(fā)展。

2023-08-04 09:40:05 321

321

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論