分頻器是數(shù)字系統(tǒng)設(shè)計(jì)中的基本電路,根據(jù)不同設(shè)計(jì)的需要,我們會(huì)遇到偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻等,有時(shí)要求等占空比,有時(shí)要求非等占空比。在同一個(gè)設(shè)計(jì)中有

2010-09-03 17:04:20 2442

2442

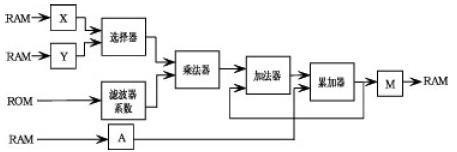

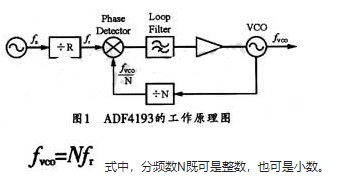

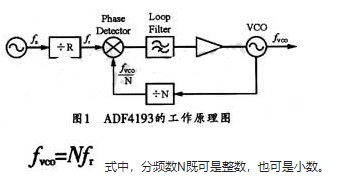

在大部分的教科書中,都會(huì)提到如何分頻,包括奇數(shù)分頻,偶數(shù)分頻,小數(shù)分頻等。 1、DDS相位累加器 (1)DDS合成流程 首先講述DSS(直接頻率合成法)的原理。 DDS是重要的頻率合成方法,在波形

2020-11-29 10:19:00 4144

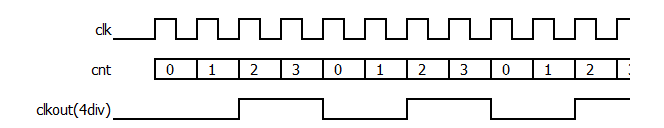

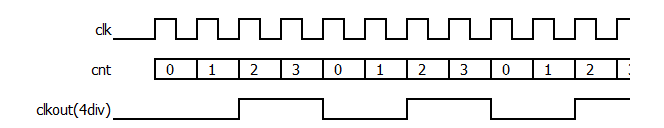

4144 前言: 偶數(shù)分頻容易得到:N倍偶數(shù)分頻,可以通過(guò)由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個(gè)復(fù)位信號(hào),使得下一個(gè)時(shí)鐘從零開始計(jì)數(shù)。以此循環(huán)下去

2020-12-28 15:49:20 2620

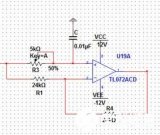

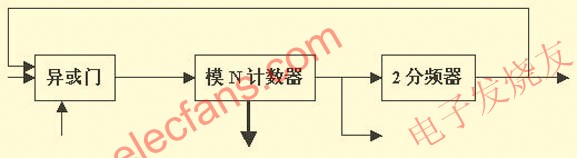

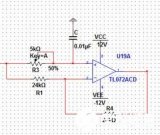

2620 。計(jì)數(shù)器進(jìn)行奇數(shù)次分頻,觸發(fā)器進(jìn)行二分頻。電路占空比為50% 1.3 濾波電路 由運(yùn)放TL072和無(wú)源元件RC組成二階有源帶通濾波電路。該電路既可以濾除直流和高次諧波分量,又可以放大電壓 1.4 移相電路 如圖-1所示,RC等幅移相電路。電路可調(diào)相范圍為0~90,幅度恒定。 圖-1 1.5 加法

2020-11-18 10:41:01 9065

9065

在進(jìn)行數(shù)字電路設(shè)計(jì)的過(guò)程中,分頻器是設(shè)計(jì)中使用頻率較高的一種基本設(shè)計(jì)之一

2023-11-07 17:29:11 745

745

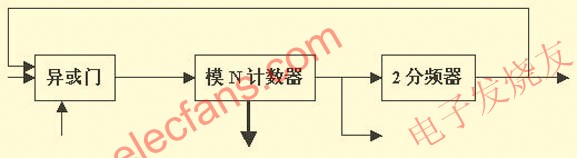

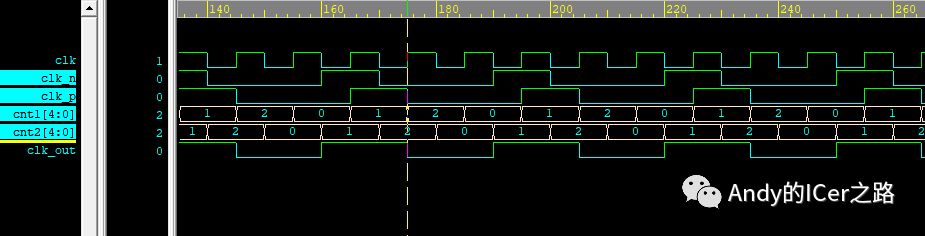

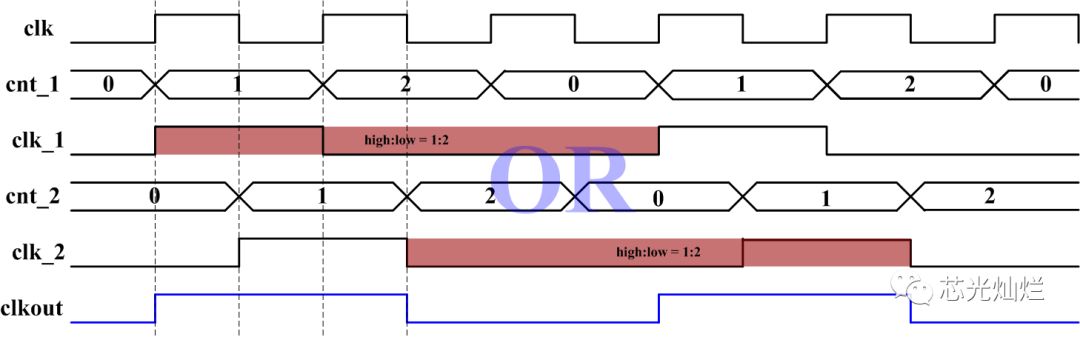

的OCC。像是拔牙操作一類的分頻我們今天不討論。今天討論的任意分頻器在許多的數(shù)字IC設(shè)計(jì)與FPGA面試筆試題中都有考察,所以在實(shí)(tou)現(xiàn)(xue)了以后做本次學(xué)習(xí)記錄,供大家參考。1. 先入為主 我們來(lái)宏觀的看本次分頻器的內(nèi)容,會(huì)比較容易理解。關(guān)鍵功能點(diǎn)的電路如圖1所示:...

2022-02-09 07:34:15

計(jì)數(shù)器一個(gè)復(fù)位信號(hào),使得下一個(gè)時(shí)鐘從零開始計(jì)數(shù)。以此循環(huán)下去。這種方法可以實(shí)現(xiàn)任意的偶數(shù)分頻。module div_6(inputi_clk,inputi_rst_n,output reg o_clk); // log2(6) = 2.5850

2013-05-01 08:44:05

D觸發(fā)器組成的_2N_1_2分頻電路,幾種奇數(shù)分頻電路設(shè)計(jì)

2012-05-23 19:34:41

`基于FPGA+的任意小數(shù)分頻器的設(shè)計(jì)基于FPGA的多種分頻設(shè)計(jì)與實(shí)現(xiàn)基于FPGA的小數(shù)分頻器的實(shí)用Verilog 實(shí)現(xiàn)基于FPGA 的通用分頻用Verilog+HDL實(shí)現(xiàn)基于FPGA的通用分頻

2012-02-03 15:02:31

等等奇數(shù)類分頻,那應(yīng)該怎么辦呢?在這里,夢(mèng)翼師兄為大家介紹一種可以實(shí)現(xiàn)任意整數(shù)分頻的方法。實(shí)現(xiàn)原理這種方法同樣也是利用了計(jì)數(shù)器來(lái)實(shí)現(xiàn),當(dāng)然我們是使用狀態(tài)機(jī)來(lái)實(shí)現(xiàn)的。我們首先定義分頻時(shí)鐘高電平的個(gè)數(shù)

2019-12-11 10:15:33

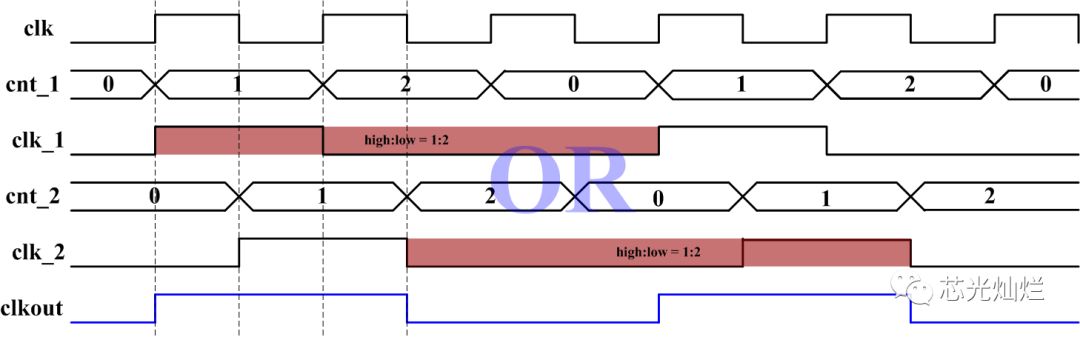

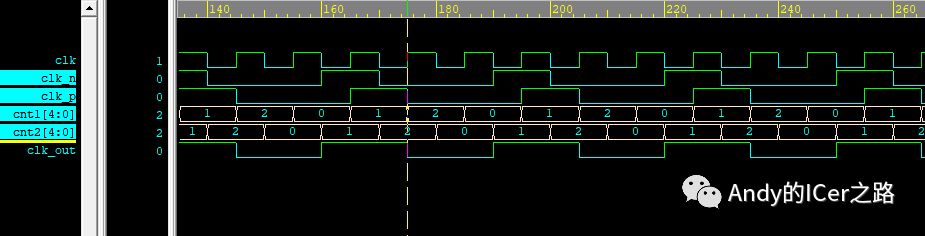

半個(gè)CLK時(shí)鐘周期。通過(guò)這兩個(gè)時(shí)鐘信號(hào)進(jìn)行邏輯運(yùn)算我們可以巧妙地得到50%占空比的時(shí)鐘。

總結(jié)如下:對(duì)于實(shí)現(xiàn)占空比為50%的N倍奇數(shù)分頻,首先進(jìn)行上升沿觸發(fā)進(jìn)行模N計(jì)數(shù),計(jì)數(shù)選定到某一個(gè)值進(jìn)行輸出時(shí)鐘

2023-12-24 18:10:59

對(duì)于分頻相信大家都不陌生了但是對(duì)于分頻的原理可能大家還不是非常清楚我在這里就談?wù)勛约旱母惺馨沙R姷奈覀兪褂玫木褪?4hc74,也就是d觸發(fā)器來(lái)做分頻。特別是對(duì)于偶數(shù)分頻一般容易使用。但是對(duì)于奇數(shù)相對(duì)來(lái)說(shuō)就比較復(fù)雜一些了下面附上我常用的的2,4分頻的電路

2009-08-04 12:10:10

觀察輸出波形并加以記錄。電路有用到:74ls90 pdf .三分頻電路d觸發(fā)器構(gòu)成2分頻電路用多級(jí)2進(jìn)計(jì)數(shù)器的分頻電路脈沖分頻電路雙穩(wěn)態(tài)分頻電路圖任意分頻電路圖1/60分頻電路用VHDL語(yǔ)言實(shí)現(xiàn)3分頻電路SN7474N構(gòu)成簡(jiǎn)單的分頻電路[此貼子已經(jīng)被作者于2009-6-22 8:04:20編輯過(guò)]

2009-06-22 08:02:10

通用的可以輸出輸入信號(hào)的2分頻信號(hào),4分頻信號(hào),8分頻信號(hào),現(xiàn)在我想產(chǎn)生3分頻信號(hào),5分頻信號(hào),如何實(shí)現(xiàn)?求指教?給個(gè)思路就行!~~

2013-11-06 23:23:05

從零開始計(jì)數(shù)。以此循環(huán)下去。這種方法可以實(shí)現(xiàn)任意的偶數(shù)分頻。第二,奇數(shù)倍分頻:奇數(shù)倍分頻常常在論壇上有人問(wèn)起,實(shí)際上,奇數(shù)倍分頻有兩種實(shí)現(xiàn)方法:首先,完全可以通過(guò)計(jì)數(shù)器來(lái)實(shí)現(xiàn),如進(jìn)行三分頻,通過(guò)待分頻時(shí)鐘

2019-06-14 06:30:00

利用變體隊(duì)列實(shí)現(xiàn)任意復(fù)雜數(shù)據(jù)集合傳遞(很方便),大家可以看看。原創(chuàng)是來(lái)自@zhihuizhou 【labview我來(lái)告訴你】實(shí)現(xiàn)任何LabVIEW數(shù)據(jù)類型集合的簡(jiǎn)潔方式。我在此基礎(chǔ)上加了一些,方便大家理解這樣的好處。

2020-02-11 15:39:21

如題,設(shè)置任意參數(shù)可變的整數(shù)分頻,分頻系數(shù)由DSP發(fā)送給CPLD,在調(diào)試的過(guò)程中發(fā)現(xiàn)由2分頻調(diào)到3分頻的時(shí)候,占空比不為50%,但是從新啟動(dòng)后的3分頻的占空比為50%,猜測(cè)應(yīng)該是計(jì)數(shù)器cnt1

2017-03-13 16:57:17

【摘要】:介紹了基于FPGA的任意分頻系數(shù)的分頻器的設(shè)計(jì),該分頻器能實(shí)現(xiàn)分頻系數(shù)和占空比均可以調(diào)節(jié)的3類分頻:整數(shù)分頻、小數(shù)分頻和分數(shù)分頻。所有分頻均通過(guò)VHDL語(yǔ)言進(jìn)行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

雙模前置小數(shù)分頻原理是什么?如何對(duì)小數(shù)分頻器進(jìn)行仿真測(cè)試?

2021-04-29 07:29:41

液晶屏漢字顯示的原理是什么?如何實(shí)現(xiàn)任意漢字的顯示?有哪些步驟?

2022-01-19 07:17:06

如何實(shí)現(xiàn)任意波形頻域變換器設(shè)計(jì)?

2022-02-15 06:30:36

如何利用DDS去實(shí)現(xiàn)任意信號(hào)波形的產(chǎn)生?怎樣設(shè)計(jì)信號(hào)源硬件電路?

2021-04-07 06:16:32

從零開始計(jì)數(shù)。以此循環(huán)下去。這種方法可以實(shí)現(xiàn)任意的偶數(shù)分頻。第二,奇數(shù)倍分頻:奇數(shù)倍分頻常常在論壇上有人問(wèn)起,實(shí)際上,奇數(shù)倍分頻有兩種實(shí)現(xiàn)方法:首先,完全可以通過(guò)計(jì)數(shù)器來(lái)實(shí)現(xiàn),如進(jìn)行三分頻,通過(guò)待分頻時(shí)鐘

2019-07-09 09:11:47

請(qǐng)問(wèn)如何采用CPLD和單片機(jī)實(shí)現(xiàn)任意波形發(fā)生器的設(shè)計(jì)?

2021-04-22 06:29:10

要設(shè)計(jì)小數(shù)分頻PLL,基本架構(gòu)已經(jīng)確定:使用基于MASH111的DSM,雙模預(yù)分頻器+PScounter實(shí)現(xiàn)。現(xiàn)在遇到的問(wèn)題是,不知道怎么把小數(shù)分頻控制字經(jīng)過(guò)DSM后的輸出與整數(shù)分頻控制字結(jié)合起來(lái)去控制(雙模分頻器+PScounter)可編程分頻器此前沒(méi)做過(guò)小數(shù)分頻PLL,求助大佬們點(diǎn)撥一二

2021-06-24 07:20:38

學(xué)校要求的課程設(shè)計(jì)基于VHDL實(shí)現(xiàn)任意小數(shù)分頻

2014-04-24 09:09:31

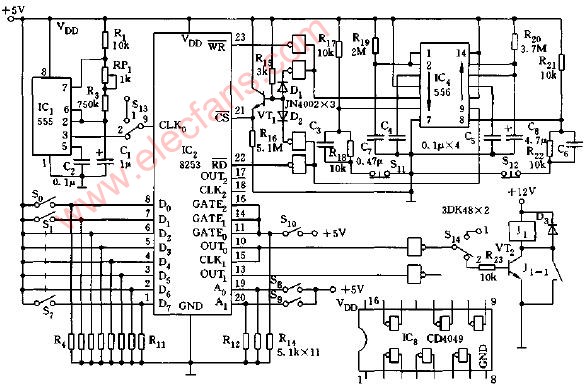

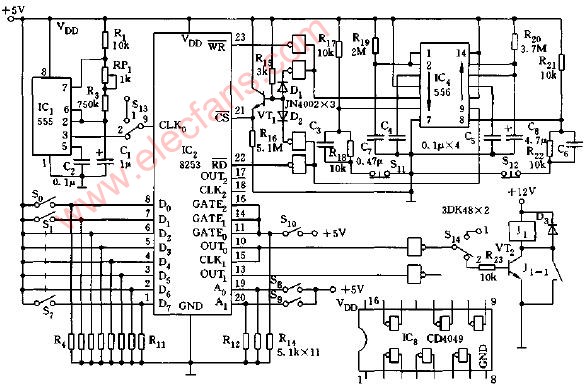

各種數(shù)字電路。包括時(shí)鐘信號(hào)產(chǎn)生電路、波形整形及變換電路、定時(shí)與延時(shí)電路、計(jì)數(shù)分頻及倍頻電路、鍵盤編碼及信號(hào)輸入電路、譯碼顯示電路、通信及數(shù)據(jù)傳輸電路、數(shù)據(jù)運(yùn)算電路、微處理器電路、存儲(chǔ)器電路···

2011-08-22 14:25:01

用verilog_hdl實(shí)現(xiàn)任意八位序列檢測(cè)

2012-08-18 10:46:48

計(jì)數(shù)器一個(gè)復(fù)位信號(hào),以使下一個(gè)時(shí)鐘從零開始計(jì)數(shù)。以此循環(huán),就可以實(shí)現(xiàn)任意的偶數(shù)分頻。 1.2 奇數(shù)倍分頻 奇數(shù)倍分頻有兩種實(shí)現(xiàn)方法,其中之一完全可以通過(guò)計(jì)數(shù)器來(lái)實(shí)現(xiàn),如進(jìn)行三分頻,就可通過(guò)待分頻

2018-10-12 16:52:21

ad9518-4,改芯片用過(guò)好多次,這次應(yīng)用不同需要輸出800MHz。發(fā)現(xiàn)如下問(wèn)題:將VCO的分頻設(shè)置0x1e0到偶數(shù)分頻(2、4)都不能鎖定。其他設(shè)置不變,設(shè)置成奇數(shù)分頻就沒(méi)有鎖不定的問(wèn)題;觀察

2018-08-19 07:53:25

. 數(shù)字電平可能容易,但是如果想實(shí)現(xiàn)模擬電平,可以嗎?

下次使用的時(shí)候,希望能夠通過(guò)編程修改這種對(duì)應(yīng)關(guān)系,同時(shí)想問(wèn)問(wèn),如果FPGA可以實(shí)現(xiàn),那么還有別的元器件可以實(shí)現(xiàn)嗎?

請(qǐng)問(wèn)CPLD或者FPGA能夠實(shí)現(xiàn)任意的IO口對(duì)聯(lián)嗎?數(shù)字方式的可以話,那么模擬方式的也可以嗎?

2023-04-23 14:19:12

目錄1、中斷向量表配置2、中斷引腳配置3、中斷處理函數(shù)EXTI0 至 EXTI15 用于 GPIO,通過(guò)編程控制可以實(shí)現(xiàn)任意一個(gè) GPIO作為 EXTI的輸入源。由表 18-1 可知, EXTI0

2021-08-13 07:26:52

本帖最后由 haozix521 于 2013-10-4 20:42 編輯

想做一個(gè)占空比50%的奇數(shù)分頻器,但是不是很了解這其中的意思。網(wǎng)上的資料都是這樣講的“對(duì)于實(shí)現(xiàn)占空比為50%的N倍奇數(shù)分頻

2013-10-04 20:35:11

任意分頻系數(shù)小數(shù)分頻器相關(guān)文檔及源代碼

2009-08-03 09:49:30 75

75 在復(fù)雜數(shù)字邏輯電路設(shè)計(jì)中,經(jīng)常會(huì)用到多個(gè)不同的時(shí)鐘信號(hào)。介紹一種通用的分頻器,可實(shí)現(xiàn)2~256 之間的任意奇數(shù)、偶數(shù)、半整數(shù)分頻。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范

2009-11-01 14:39:19 78

78 該文提出采用信號(hào)流圖實(shí)現(xiàn)任意階FTFN-RC 通用濾波器的方法。通過(guò)對(duì)網(wǎng)絡(luò)函數(shù)的直接分析,導(dǎo)出了任意階傳輸函數(shù)的FTFN-RC 實(shí)現(xiàn)電路。該濾波電路僅包含n 個(gè)有源器件,n 個(gè)接地電容和

2010-02-09 15:10:30 27

27 基于FPGA 的等占空比任意整數(shù)分頻器的設(shè)計(jì)

給出了一種基于FPGA 的等占空比任意整數(shù)分頻電路的設(shè)計(jì)方法。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 提出了一種通用的可編程雙模分頻器,電路主要由3 部分組成: 9/8 預(yù)分頻器,8 位可編程計(jì)數(shù)器和ΣΔ調(diào)制器構(gòu)成。通過(guò)打開或者關(guān)斷ΣΔ 調(diào)制器的輸出來(lái)實(shí)現(xiàn)分?jǐn)?shù)和整數(shù)分頻兩種工作

2010-04-23 08:39:35 30

30 議程PLL介紹及小數(shù)分頻鎖相環(huán)的優(yōu)點(diǎn)小數(shù)分頻鎖相環(huán)的錯(cuò)誤使用小數(shù)分頻鎖相環(huán)詳解參考雜散及如何減少雜散總結(jié)

2010-05-28 14:58:36 0

0 用VHDL語(yǔ)言實(shí)現(xiàn)3分頻電路

標(biāo)簽/分類:

眾所周知,分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

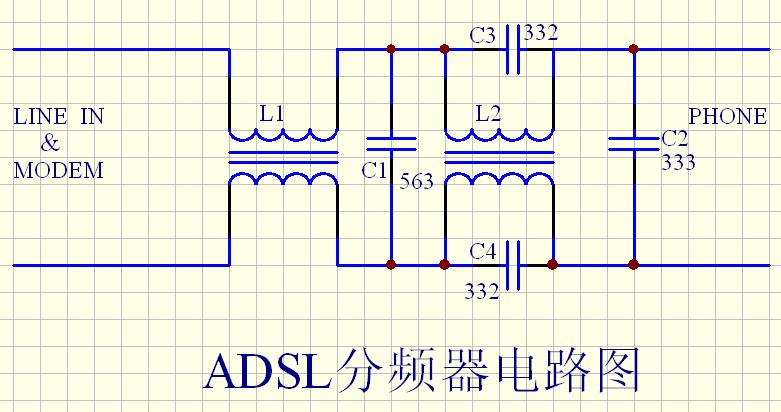

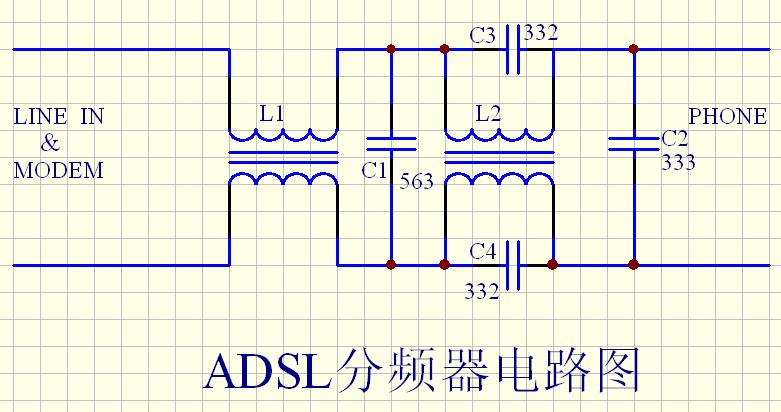

5527 ADSL分頻器電路圖從電路上可以看出,該分頻器的作用只是針對(duì)電話座機(jī),而非針對(duì)MODEM。在一般

2007-09-30 19:53:24 2148

2148

IIR數(shù)字濾波器設(shè)計(jì)-在FPGA上實(shí)現(xiàn)任意階IIR數(shù)字濾波器

摘 要:本文介紹了一種采用級(jí)聯(lián)結(jié)構(gòu)在FPGA上實(shí)現(xiàn)任意階IIR數(shù)字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

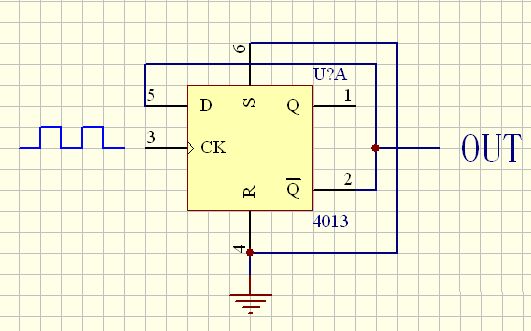

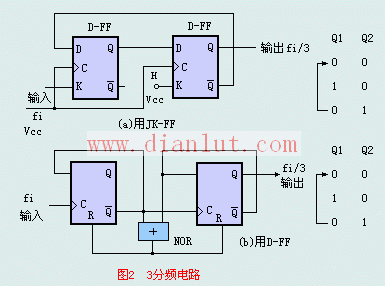

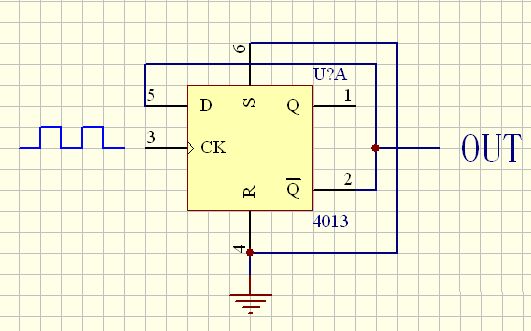

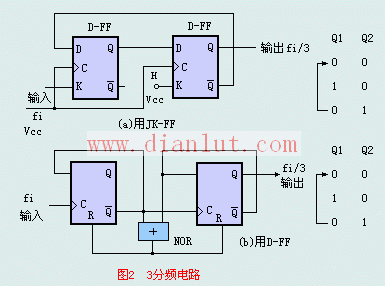

下圖是 用于N=二-四分頻比的電路,常用雙D-FF或雙JK-FF器件來(lái)構(gòu)成,分頻比n>4的電路,則常采用計(jì)數(shù)器(如可預(yù)置計(jì)數(shù)器)來(lái)實(shí)現(xiàn)更為方便,一般無(wú)需再用單個(gè)FF來(lái)組合。

2008-06-29 23:31:06 22462

22462

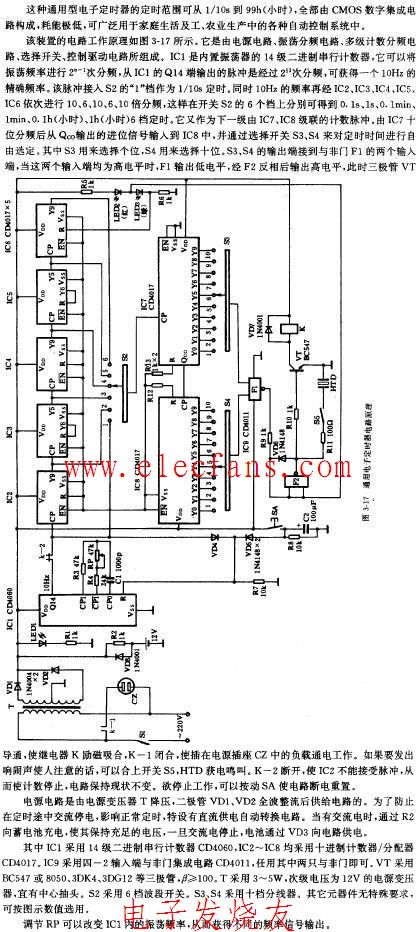

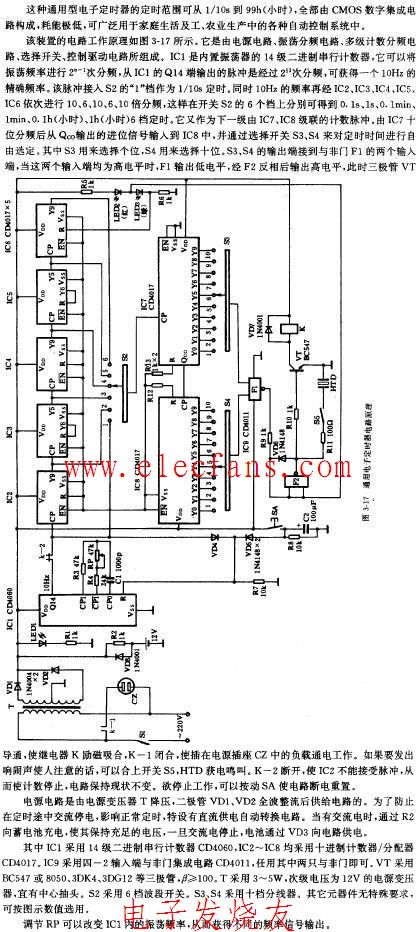

通用電子定時(shí)器電路圖

2008-08-11 08:26:07 5094

5094

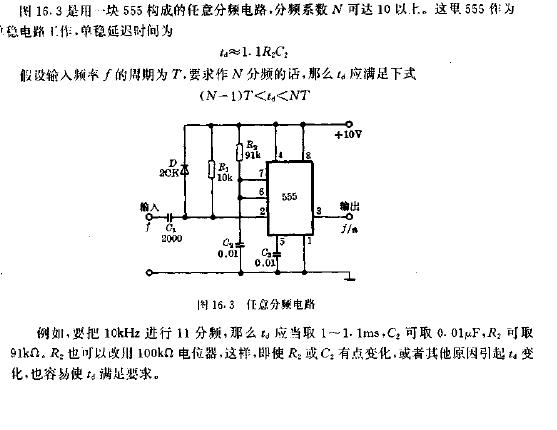

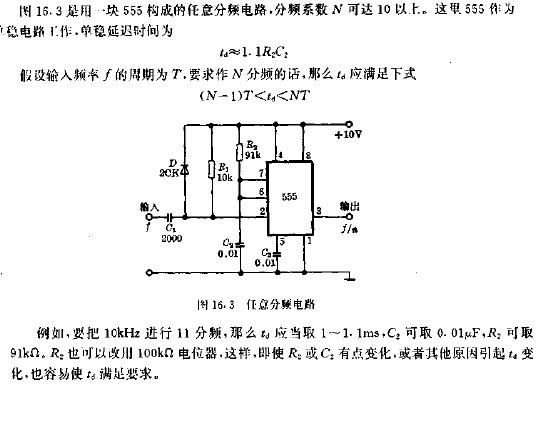

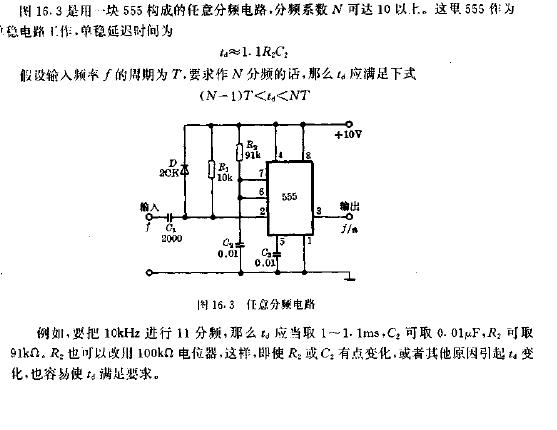

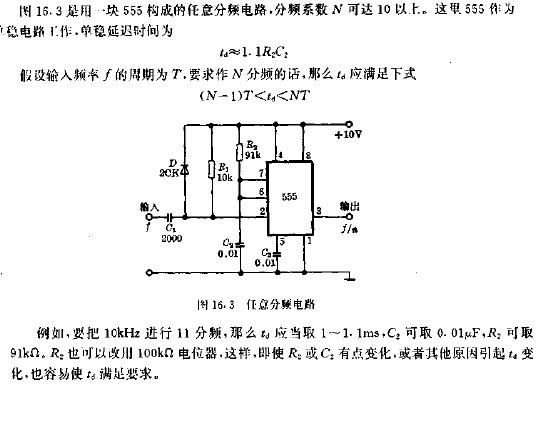

任意分頻電路圖

2009-04-09 12:02:35 2758

2758

可編程定時(shí)、分頻兩用電路圖

2009-05-30 15:57:39 485

485

D觸發(fā)器實(shí)現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)&

2009-06-12 13:58:56 75438

75438

分頻電路

在一個(gè)揚(yáng)聲器系統(tǒng)里,人們把箱體、分頻電路、揚(yáng)聲器單元稱為揚(yáng)聲器系統(tǒng)的三大件,而分頻電路對(duì)揚(yáng)聲器系統(tǒng)能否高質(zhì)量地還原電聲信號(hào)起著

2009-06-12 14:35:10 6578

6578

摘 要: 本文通過(guò)在QuartursⅡ開發(fā)平臺(tái)下,一種能夠實(shí)現(xiàn)等占空比、非等占空比整數(shù)分頻及半整數(shù)分頻的通用分頻器的FPGA設(shè)計(jì)與實(shí)現(xiàn),介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

圖2是3分頻電路,用JK-FF實(shí)現(xiàn)3分頻很方便,不需要附加任何邏輯電路就能實(shí)現(xiàn)同步計(jì)數(shù)分頻。但用D-FF實(shí)現(xiàn)3分頻時(shí),必須附加譯碼反饋電路,如圖2所示的譯碼復(fù)位電路,強(qiáng)制計(jì)數(shù)狀態(tài)

2009-06-22 07:41:00 12116

12116

什么是分頻電路

2009-06-22 07:51:22 5386

5386

10分頻電路

任意分頻電路圖

2009-06-22 08:04:33 15654

15654

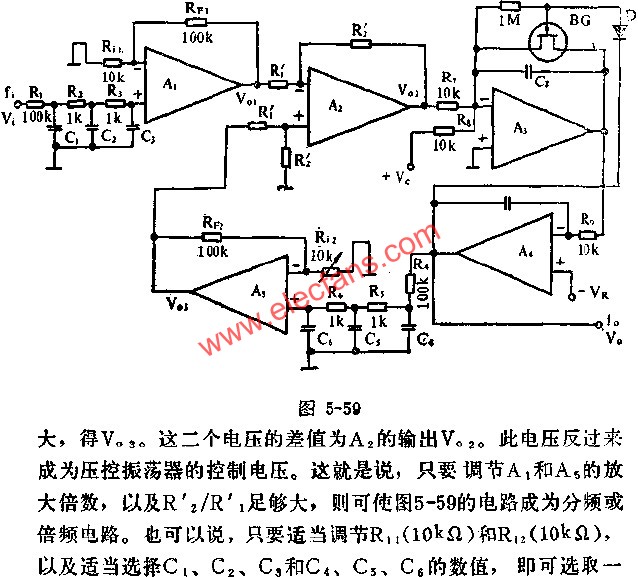

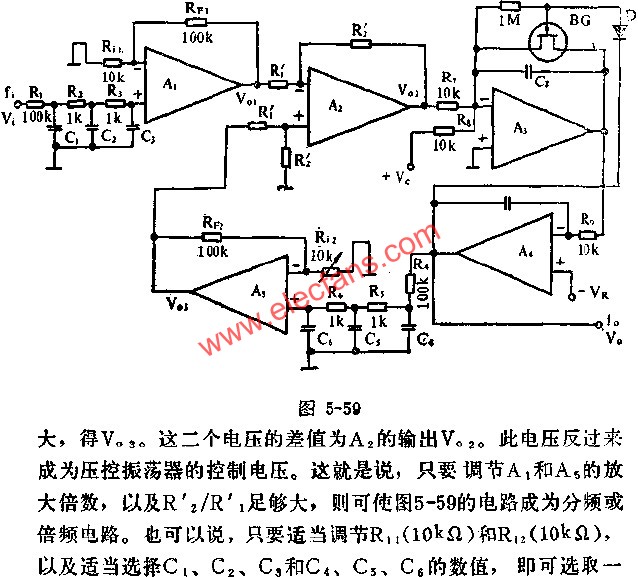

圖中所示是用運(yùn)算放大器通用I型組成的分頻和倍頻電路.能在10HZ~10KHZ頻段內(nèi)工作.圖示線路是分頻與倍頻的基本

2010-10-08 12:12:21 10528

10528

給出了一種小數(shù)分頻技術(shù)的實(shí)現(xiàn)方法, 并在實(shí)驗(yàn)的基礎(chǔ)上進(jìn)一步證實(shí)了小數(shù)分頻的可行性該法通過(guò)微機(jī)控制,

2011-02-22 14:58:54 45

45 在電子技術(shù)中,N/2(N為奇數(shù))分頻電路有著重要的應(yīng)用.對(duì)一個(gè)特定輸入頻率,要經(jīng)N/2分頻后才能得到所需要的輸出,這就要求電路具有N/2的非整數(shù)倍的分頻功能。CD4013是雙D觸發(fā)器,在以CIM013為主組成的若干個(gè)二分頻電路的基礎(chǔ)上,加上異或門等反饋控{6I,即

2011-03-11 17:05:45 338

338 提出了一種基于FPGA的小數(shù)分頻實(shí)現(xiàn)方法,介紹了現(xiàn)有分頻方法的局限性,提出一種新的基于兩級(jí)計(jì)數(shù)器的分頻實(shí)現(xiàn)方法,給出了該設(shè)計(jì)方法的設(shè)計(jì)原理以及實(shí)現(xiàn)框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數(shù)分頻器的分頻原理及電路設(shè)計(jì),并用VHDL編程實(shí)現(xiàn)分頻器的仿真.

2011-11-29 16:43:06 48

48 Delphi教程之在DBGrid中實(shí)現(xiàn)任意方向查找,學(xué)習(xí)Delphi的必備資料。

2016-03-31 11:29:41 3

3 用 Verilog實(shí)現(xiàn)基于FPGA 的通用分頻器的設(shè)計(jì)時(shí)鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 45

45 原文出自:分頻器是指使輸出信號(hào)頻率為輸入信號(hào)頻率整數(shù)分之一的電子電路。在許多電子設(shè)備中如電子鐘、頻率合成器等,需要各種不同頻率的信號(hào)協(xié)同工作,常用的方法是以穩(wěn)定度高的晶體振蕩器為主振源,通過(guò)變換得到所需要的各種頻率成分,分頻器是一種主要變換手段。

2017-02-11 04:04:11 14086

14086

受外部周期信號(hào)激勵(lì)的震蕩,其頻率恰為激勵(lì)信號(hào)頻率的純分?jǐn)?shù),都叫做分頻。實(shí)現(xiàn)分頻的電路或裝置稱為“分頻器”。(純分?jǐn)?shù):只有分?jǐn)?shù)部分,即小于1的分?jǐn)?shù),如3/4就是,而一又五分之四(1+4/5)就不是。)

2017-11-02 10:53:02 35807

35807 三分頻,五分頻,七分頻等等奇數(shù)類分頻,那究竟怎么辦呢?在這里,讓我介紹一個(gè)可以實(shí)現(xiàn)任意整數(shù)分頻的方法,這個(gè)辦法也是同樣利用了計(jì)數(shù)器來(lái)計(jì)算,當(dāng)是跟偶數(shù)分頻不一樣的地方是任意整數(shù)分頻利用了兩個(gè)計(jì)數(shù)器來(lái)實(shí)現(xiàn)。 設(shè)計(jì)原理 : 本

2018-06-13 11:21:48 12390

12390

三分頻電路,在電路圖中,在一般的利用常規(guī)計(jì)數(shù)器對(duì)數(shù)字脈沖進(jìn)行奇數(shù)分頻時(shí),即使輸入是對(duì)稱信號(hào), 輸出也得不到占空比為50%的分頻輸出,其原因是內(nèi)部觸發(fā)器采用的是統(tǒng)一的上升沿(或下降沿)進(jìn)行觸發(fā)。

2018-08-13 11:08:34 110927

110927

小數(shù)分頻是頻率合成中的一項(xiàng)新技術(shù)。這種技術(shù)的特點(diǎn)是使單環(huán)鎖相頻率合成器的平均分頻比變?yōu)樾?shù)。通過(guò)使分頻比變?yōu)樾?shù),可獲得任意小的頻率間隔,實(shí)現(xiàn)高頻率分辨力的頻率合成,利用小數(shù)分頻技術(shù)完成的小數(shù)分頻頻率合成器,不僅頻率分辨力高,而且頻率轉(zhuǎn)換速度快,還可使頻譜改善、線路簡(jiǎn)化、體積縮小、程控方便、集成容易。

2019-05-24 08:05:00 1639

1639

關(guān)鍵詞:74LS109 , 74LS113 , 分頻電路 如圖所示為對(duì)稱輸出的三分頻電路。在一般的利用常規(guī)計(jì)數(shù)器對(duì)數(shù)字脈沖進(jìn)行奇數(shù)分頻時(shí).即使輸入是對(duì)稱信號(hào),輸出也得不到占空比為50%的分頻輸出

2018-09-28 09:47:01 1726

1726 需要進(jìn)行調(diào)整。輸入脈沖是一束一束斷續(xù)的。經(jīng)過(guò)第一級(jí)二分頻電路后,雖然對(duì)束內(nèi)的脈沖進(jìn)行了分頻,但在束與柬脈沖的間隙期間既可能處于低電平(如果束內(nèi)脈沖為偶數(shù)個(gè)),也可能處于高電平(如果束內(nèi)脈沖為奇數(shù)個(gè)),所以在后面加了單穩(wěn)態(tài)電路

2018-10-03 18:12:06 1354

1354 關(guān)鍵詞:MC4018 , 分頻器 如圖所示為數(shù)控分頻電路。 圖(a)為數(shù)控分頻器原理圖。它可以做到任意分頻系數(shù)且輸出為對(duì)稱方波。對(duì)于任意一個(gè)偶數(shù)N,可以寫成N=2M,而對(duì)于任意一個(gè)奇數(shù)N,則可

2018-10-03 18:23:01 526

526 分頻器主要分為偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻和小數(shù)分頻,如果在設(shè)計(jì)過(guò)程中采用參數(shù)化設(shè)計(jì),就可以隨時(shí)改變參量以得到不同的分頻需要。

2019-02-01 01:28:00 15719

15719

分頻器是一種基本電路,通常用來(lái)對(duì)某個(gè)給定頻率進(jìn)行分頻,得到所需的頻率。整數(shù)分頻器的實(shí)現(xiàn)非常簡(jiǎn)單,可采用標(biāo)準(zhǔn)的計(jì)數(shù)器,也可以采用可編邏輯器件設(shè)計(jì)實(shí)現(xiàn)。但在某些場(chǎng)合下,時(shí)鐘源與所需的頻率不成整數(shù)倍關(guān)系,此時(shí)可采用小數(shù)分頻器進(jìn)行分頻。

2019-11-20 07:05:00 6652

6652 論文分析了雙模前置小數(shù)分頻器的分頻原理和電路實(shí)現(xiàn)。結(jié)合脈沖刪除技術(shù),提出了一種適于硬件電路實(shí)現(xiàn)的任意小數(shù)分頻的設(shè)計(jì)方案 ,用 VerilogHDL語(yǔ) 言編程 ,在 QuartusII下對(duì) 此方案進(jìn) 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片來(lái) 實(shí) 現(xiàn) 。

2019-08-02 08:00:00 5

5 在數(shù)字系統(tǒng)設(shè)計(jì)中,根據(jù)不同的設(shè)計(jì)需要,經(jīng)常會(huì)遇到偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻等,有的還要求等占空比。在基于cpld(復(fù)雜可編程邏輯器件)的數(shù)字系統(tǒng)設(shè)計(jì)中,很容易實(shí)現(xiàn)由計(jì)數(shù)器或其級(jí)聯(lián)構(gòu)成各種形式的偶數(shù)分頻及非等占空比的奇數(shù)分頻,但對(duì)等占空比的奇數(shù)分頻及半整數(shù)分頻的實(shí)現(xiàn)較為困難。

2020-06-26 09:36:00 825

825

時(shí)間段就變成了0.5個(gè)周期,就不能通過(guò)clk的計(jì)數(shù)直接實(shí)現(xiàn)了。 然而,時(shí)鐘信號(hào)的上升沿和下降沿之間正好相差0.5個(gè)周期,利用這個(gè)就可以實(shí)現(xiàn)奇數(shù)分頻啦 第一步:分別使用原時(shí)鐘上升沿和下降沿產(chǎn)生兩個(gè)計(jì)數(shù)器(基于上升沿計(jì)數(shù)的cnt1和基于下降沿計(jì)數(shù)的cnt2),計(jì)數(shù)器在

2021-03-12 15:44:54 5614

5614

一種新型的采用電流轉(zhuǎn)向電荷泵的快速鎖定小數(shù)分頻鎖相環(huán)介紹。

2021-05-08 10:55:08 5

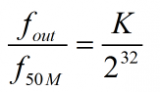

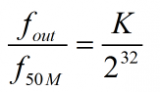

5 分頻器是用的最廣的一種FPGA電路了,我最初使用的是crazybingo的一個(gè)任意分頻器,可以實(shí)現(xiàn)高精度任意分頻的一個(gè)通用模塊,他的思想在于首先指定計(jì)數(shù)器的位寬比如32位,那么這個(gè)計(jì)數(shù)器的最大值就是

2021-06-13 17:11:00 4513

4513

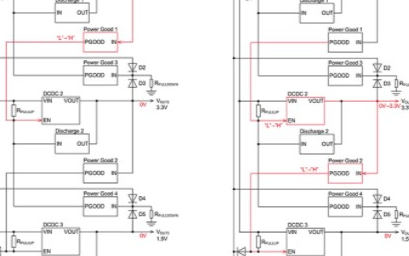

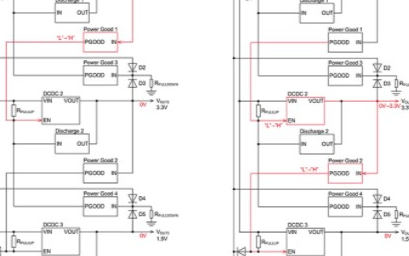

上一篇文章中介紹了使用通用電源IC實(shí)現(xiàn)電源時(shí)序控制電路的“電源時(shí)序規(guī)格①”的控制電路。本文先介紹使用通用電源IC實(shí)現(xiàn)電源時(shí)序控制電路中,電源導(dǎo)通時(shí)的時(shí)序工作。

2022-01-18 14:50:21 4422

4422

有關(guān)小數(shù)分頻的資料,用于時(shí)鐘芯片設(shè)計(jì),十分經(jīng)典。

2022-10-24 11:48:44 0

0 在verilog程序設(shè)計(jì)中,我們往往要對(duì)一個(gè)頻率進(jìn)行任意分頻,而且占空比也有一定的要求這樣的話,對(duì)于程序有一定的要求,現(xiàn)在我在前人經(jīng)驗(yàn)的基礎(chǔ)上做一個(gè)簡(jiǎn)單的總結(jié),實(shí)現(xiàn)對(duì)一個(gè)頻率的任意占空比的任意分頻。

2023-01-05 09:33:41 1606

1606 “使用通用電源IC實(shí)現(xiàn)電源時(shí)序控制的電路”系列文章已經(jīng)發(fā)表了11篇,本文是使用通用電源IC實(shí)現(xiàn)電源時(shí)序控制的電路的最后一篇。

2023-02-23 10:40:58 900

900 所謂“分頻”,就是把輸入信號(hào)的頻率變成成倍數(shù)地低于輸入頻率的輸出信號(hào)。數(shù)字電路中的分頻器主要是分為兩種:整數(shù)分頻和小數(shù)分頻。其中整數(shù)分頻又分為偶分頻和奇分頻,首先從偶分頻開始吧,入門先從簡(jiǎn)單的開始!

2023-03-23 15:06:22 948

948

上一篇文章介紹了偶分頻,今天來(lái)介紹一下奇數(shù)分頻器的設(shè)計(jì)。

2023-03-23 15:06:49 692

692

前面分別介紹了偶數(shù)和奇數(shù)分頻(即整數(shù)分頻),接下來(lái)本文介紹小數(shù)分頻。

2023-03-23 15:08:04 658

658

初學(xué) Verilog 時(shí)許多模塊都是通過(guò)計(jì)數(shù)與分頻完成設(shè)計(jì),例如 PWM 脈寬調(diào)制、頻率計(jì)等。而分頻邏輯往往通過(guò)計(jì)數(shù)邏輯完成。本節(jié)主要對(duì)偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻以及小數(shù)分頻進(jìn)行簡(jiǎn)單的總結(jié)。

2023-03-29 11:38:40 3108

3108

時(shí)鐘分頻電路(分頻器)在IC設(shè)計(jì)中經(jīng)常會(huì)用到,其目的是產(chǎn)生不同頻率的時(shí)鐘,滿足系統(tǒng)的需要。 比如一個(gè)系統(tǒng),常規(guī)操作都是在1GHz時(shí)鐘下完成,突然要執(zhí)行一個(gè)操作涉及到模擬電路,所需時(shí)間是us量級(jí)的,顯然用1GHz(周期是1ns)的時(shí)鐘進(jìn)行操作是不合適的。

2023-04-25 14:46:25 5332

5332

上一篇文章時(shí)鐘分頻系列——偶數(shù)分頻/奇數(shù)分頻/分數(shù)分頻,IC君介紹了各種分頻器的設(shè)計(jì)原理,其中分數(shù)分頻器較為復(fù)雜,這一篇文章IC君再跟大家聊聊分數(shù)分頻的具體設(shè)計(jì)實(shí)現(xiàn)。

2023-04-25 14:47:44 1028

1028

入門從簡(jiǎn)單開始,先來(lái)個(gè)三分頻分析一下。三分頻其實(shí)就是把輸入時(shí)鐘的三個(gè)周期當(dāng)作一個(gè)周期,具體波形如圖所示。

2023-06-05 16:57:23 753

753

對(duì)于要求相位以及占空比嚴(yán)格的小數(shù)分頻,建議采用模擬電路實(shí)現(xiàn)。而使用數(shù)字電路實(shí)現(xiàn)只能保證盡量均勻,在長(zhǎng)時(shí)間內(nèi)進(jìn)行分頻。

2023-06-05 17:20:51 969

969

是用于滿足設(shè)計(jì)的需求。 分頻:產(chǎn)生比板載時(shí)鐘小的時(shí)鐘。 倍頻:產(chǎn)生比板載時(shí)鐘大的時(shí)鐘。 二:分頻器的種類 對(duì)于分頻電路來(lái)說(shuō),可以分為整數(shù)分頻和小數(shù)分頻。 整數(shù)分頻:偶數(shù)分頻和奇數(shù)分頻。 小數(shù)分頻:半整數(shù)分頻和非半整數(shù)分頻。 三:分頻器的思想 采用計(jì)數(shù)器的思想實(shí)

2023-11-03 15:55:02 471

471

其實(shí)這個(gè)分頻時(shí)鐘切換很簡(jiǎn)單,根本不需要額外的切換電路。一個(gè)共用的計(jì)數(shù)器,加一點(diǎn)控制邏輯,就可以了,而且可以實(shí)現(xiàn)2到16任意整數(shù)分頻率之間的無(wú)縫切換。

2023-12-14 15:28:56 257

257

鎖相環(huán)整數(shù)分頻和小數(shù)分頻的區(qū)別是什么? 鎖相環(huán)(PLL)是一種常用的電子電路,用于將輸入的時(shí)鐘信號(hào)與參考信號(hào)進(jìn)行同步,并生成輸出信號(hào)的一種技術(shù)。在PLL中,分頻器模塊起到關(guān)鍵作用,可以實(shí)現(xiàn)整數(shù)分頻

2024-01-31 15:24:48 312

312

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論