介紹一種基于CPLD和嵌入式系統的高速數據采集系統,并詳細闡述了系統的結構和軟硬件的實現方案。

關鍵詞:高速數據采集;CPLD;嵌入式系統

Design and Implementation of High?speed Data Sampling System Ba sed on

CPLD and Embedded System

CPLD and Embedded System

LIN Dehui, DAO Kegang, DENG Yonggang, CHEN Sen

Key words: high?speed data sampling; CPLD; embedded system

1系統結構

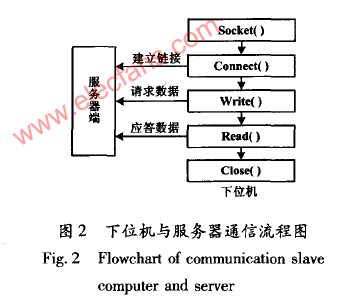

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

2.1嵌入式操作系統—Linux

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

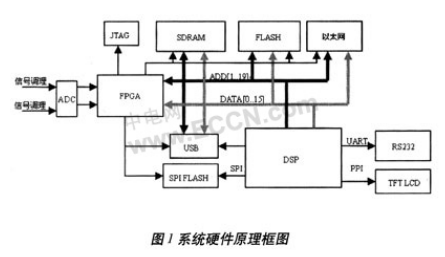

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

嵌入式系統的CPU選用Motorola的MPC860芯片。它內部集成了微處理器和一些控制領域的常用外圍組件,特別適用于互聯網絡和數據通信。MPC860 PowerQUICC通信處理器可以根據用戶的不同要求提供2~4個串行通信控制器、數據緩存,各種級別的網絡協議支持。該處理器專為寬帶接入設備如路由器、集線器、交換機和網關等設計。

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASE?T的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。

2.2.7FIFO數據緩存電路

從圖1可以看出,系統中包含兩級FIFO。第一級FIFO芯片采用1片CY7C4251,容量為8KB×9bit,工作頻率為100MHz。第二級FIFO采用2片CY7C4255并聯,容量為8KB×36bit,但實際上只用了24bit數據寬度,因為8bit的A/D轉換數據累加10000次,24bit就能滿足系統的功能要求。

2.3軟件開發

該數據采集系統的軟件編程包括兩部分,一部分是MPC860嵌入式系統的編程;另一部分是CPLD的編程。關于CPLD的編程模式見2.2.6,這里只介紹嵌入式系統的軟件開發模式。

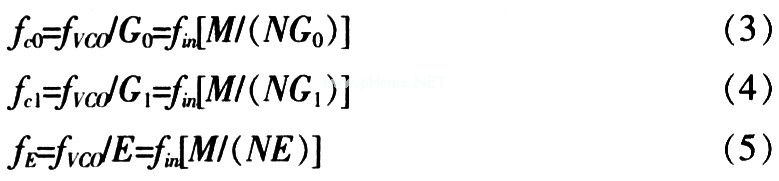

本系統采用交叉編譯的方式進行Linux應用程序的開發和調試,先將應用程序在宿主機上調試通過后,再移植到目標板。這種模式適合于大型復雜的應用,優點是程序調試方便但移植需要做一些工作。其開發流程如圖3所示。

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASE?T的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。

2.2.7FIFO數據緩存電路

從圖1可以看出,系統中包含兩級FIFO。第一級FIFO芯片采用1片CY7C4251,容量為8KB×9bit,工作頻率為100MHz。第二級FIFO采用2片CY7C4255并聯,容量為8KB×36bit,但實際上只用了24bit數據寬度,因為8bit的A/D轉換數據累加10000次,24bit就能滿足系統的功能要求。

2.3軟件開發

該數據采集系統的軟件編程包括兩部分,一部分是MPC860嵌入式系統的編程;另一部分是CPLD的編程。關于CPLD的編程模式見2.2.6,這里只介紹嵌入式系統的軟件開發模式。

本系統采用交叉編譯的方式進行Linux應用程序的開發和調試,先將應用程序在宿主機上調試通過后,再移植到目標板。這種模式適合于大型復雜的應用,優點是程序調試方便但移植需要做一些工作。其開發流程如圖3所示。

系統總的工作過程為:由MPC860發送一個START高電平給EPM3128,EPM3128接收到此信號后,產生2000個10ns的脈沖信號給ADC08200,采樣后的數據存放在CY7C4251中。EPM3128產生CY7C4251的讀脈沖依次讀取FIFO中的數據并將其與從CY7C4255中取來的24位數據相加后再送回到CY7C4255中,每次累加在40ns中完成。這樣循環10000次,就完成了數據的累加。累加完成后,EPM3128發送IRQ中斷請求信號至MPC860,MPC860響應中斷在IO口上產生READ低電平讀信號,CPLD產生CY7C4255的讀使能信號將數據讀出送至三態緩沖器74F245,MPC860讀取數據時發送OE信號選通數據三態緩沖器74F245將數據讀出至MPC860數據總線,接收完數據通過 網口將數據發送給上位機處理。累加結果的讀取過程如圖4所示。

本文介紹的高速數據采集系統實現了分布式光纖溫度傳感器測溫系統中噪聲的有效抑制,具 有速度快、可靠性高的特點。另外由于CPLD的可編程性,可以對該電路板加以改造用在其他 的高速數據采集場合。

- 數據采集(112246)

相關推薦

5 Gsps高速數據采集系統該怎么設計?

高速實時頻譜儀是對實時采集的數據進行頻譜分析,要達到這樣的目的,對數據采集系統的采樣精度、采樣率和存儲量等指標提出了更高的要求。而在高速數據采集系統中,ADC在很大程度上決定了系統的整體性能,而它們的性能又受到時鐘質量的影響。

2019-09-02 06:44:39

嵌入式系統采集圖像數據的遠程測量有什么優點?

隨著后PC時代的到來和嵌入式的蓬勃發展,運用嵌入式系統實現遠程數據采集已成為社會需求的趨勢。本文采用嵌入式系統采集圖像數據實現加工零件的遠程測量,代替傳統的人工檢測。其特點有:網絡化,準確性高,節約人力和物力。

2019-08-30 07:23:15

嵌入式系統怎么實現遠程監控和升級?

通用分組無線服務技術GPRS(General Packet Radio Service)是一種移動數據業務,該技術能滿足日常網絡行為,具有廣域覆蓋、高速傳輸等優點。野外作業的數據采集嵌入式系統工作于

2019-08-02 06:49:24

嵌入式單片機視頻報警系統的工作原理是什么?

利用以單片機應用系統為中心的小型嵌入式設備進行數據采集,并通過網絡有效傳輸數據,已成為數據采集領域的研究焦點。由于嵌入式單片機系統集單片機和嵌入式系統為一體,因此嵌入式單片機系統廣泛應用于那些對實時

2019-10-21 08:31:14

嵌入式多路信號數據采集系統有什么功能?

由于人們對數字形式信息的需求量越來越大,數據采集及其應用技術受到了越來越廣泛的關注和應用。隨著技術的發展,數據采集系統正向著高精度、高速度、穩定可靠和集成化的方向發展。目前,大多數的數據采集監控系統

2020-03-17 08:24:26

嵌入式電能計量及查詢系統有什么功能?

本文設計了一個既能接入宿舍電量采集系統又能接入校內 Intranet 信息網絡的嵌入式電能計量及查詢系統,在電能數據采集終端 (ERTU)采用嵌入式ARM2410 芯片和嵌入式實時操作系統Linux

2019-09-26 07:08:15

嵌入式網絡接入怎么實現?

的說法。利用該技術可以實現基于Internet的遠程數據采集、遠程控制、自動報警等功能,大大擴展嵌入式設備的應用范圍;同時充分利用網絡資源,實現更廣泛的信息共享和更多信息服務。研究顯示,截止2010年

2020-03-19 06:30:03

嵌入式視覺系統開發過程有什么技巧?

目前,關于視覺系統的研究已經成為熱點,也有開發出的系統可供參考。但這些系統大多是基于PC機的,由于算法和硬件結構的復雜性而使其在小型嵌入式系統中的應用受到了限制。上述系統將圖像數據采集后,視覺處理

2019-08-15 06:15:37

嵌入式視頻數據采集的主要過程是什么?

卡驅動程序,V4L可以實現影像采集、AM/FM無線廣播、影像CODEC、頻道切換等功能。目前,V4L主要應用在影像串流系統與嵌入式影像系統里,其應用范圍相當廣泛。

2019-08-14 07:28:23

數據采集卡/分布式采集模塊/無線通訊采集模塊/嵌入式系統

無線通訊數據采集模塊:GPRSZIGBEE4. 嵌入式系統:嵌入式主板平板電腦工控一體機QQ2693330939郵箱2693330939@qq.com 電話:*** 聯系人江莽

2014-08-21 10:05:12

高速數據采集系統的硬件結構,CPLD在高速數據采集系統中的應用

高速數據采集系統的硬件結構MAX7000系列CPLD及其開發平臺介紹CPLD在高速數據采集系統中的應用

2021-04-08 06:11:56

電子發燒友App

電子發燒友App

評論