Chiplets的主導(dǎo)地位才剛剛開始。

Chiplets已經(jīng)使用了幾十年,但它們之前一直被用于少量特殊的用途。現(xiàn)在,它們處于技術(shù)的最前沿,全世界有數(shù)百萬人在臺(tái)式電腦、工作站和服務(wù)器中使用它們。 處理器行業(yè)領(lǐng)導(dǎo)者利用Chiplets重新站在了創(chuàng)新的最前沿,可以預(yù)見未來Chiplets將成為計(jì)算世界的標(biāo)準(zhǔn)之一。因此,有必要了解Chiplets以及它們?nèi)绱酥匾拇_切原因。 ?

什么是Chiplets? ?

Chiplets是分隔式的處理器。不是將每個(gè)部分合并到一個(gè)芯片中(被稱為單片機(jī)的方法),而是將特定的部分作為獨(dú)立的芯片來制造。

然后,這些獨(dú)立的芯片通過一個(gè)復(fù)雜的連接系統(tǒng)被安裝在一起,成為一個(gè)單一的封裝。 這種安排使能夠讓使用最新的制造方法的部件尺寸縮小,提高了工藝的效率,使其能夠裝入更多的部件。

芯片中不能明顯縮小或不需要縮小的部分可以用更舊的、更經(jīng)濟(jì)的方法生產(chǎn)。

雖然制造這種處理器的過程很復(fù)雜,但總體成本通常較低。此外,它為處理器公司提供了一個(gè)更易于管理的途徑來擴(kuò)大其產(chǎn)品范圍。

為了充分理解為什么處理器制造商轉(zhuǎn)向芯片,我們必須首先深入了解這些設(shè)備是如何制造的。

CPU和GPU開始時(shí)是由超純硅制成的大圓盤,通常直徑略小于12英寸(300毫米),厚度為0.04英寸(1毫米)。

這塊硅片經(jīng)歷了一系列復(fù)雜的步驟,形成了不同材料的多層--絕緣體、電介質(zhì)和金屬。這些層的圖案是通過一種叫做光刻的工藝創(chuàng)建的,在這種工藝中,紫外線通過放大的圖案(掩膜)照射,隨后通過透鏡縮小到所需的尺寸。該圖案以設(shè)定的間隔在晶圓表面重復(fù)出現(xiàn),每一個(gè)都將最終成為一個(gè)處理器。

由于芯片是長方形的,而晶圓是圓形的,圖案必須與圓盤的周邊重疊。這些重疊的部分最終會(huì)被丟棄,因?yàn)樗鼈兪菬o功能的。

一旦完成,將使用應(yīng)用于每個(gè)芯片的探針對(duì)晶圓進(jìn)行測(cè)試。電檢結(jié)果告知工程師關(guān)于處理器的質(zhì)量與一長串標(biāo)準(zhǔn)的關(guān)系。這個(gè)初始階段被稱為芯片分選,有助于確定處理器的 "等級(jí)"。

例如,如果該芯片打算成為一個(gè)CPU,那么每個(gè)部分都應(yīng)該正確運(yùn)作,在特定的電壓下在設(shè)定的時(shí)鐘速度范圍內(nèi)運(yùn)行。然后根據(jù)這些測(cè)試結(jié)果對(duì)每個(gè)晶圓部分進(jìn)行分類。

完成后,晶圓被切割成單獨(dú)的碎片,或稱 "模具",可供使用。然后,這些模具被安裝在一個(gè)基板上,類似于一個(gè)專門的主板。

處理器經(jīng)過進(jìn)一步的包裝(例如,用散熱器),然后就可以進(jìn)行銷售了。整個(gè)過程可能需要數(shù)周的制造時(shí)間,臺(tái)積電和三星等公司對(duì)每個(gè)晶圓收取高額費(fèi)用,根據(jù)所使用的工藝節(jié)點(diǎn),費(fèi)用在3000至20000美元之間。 "工藝節(jié)點(diǎn) "(Process node)是用來描述整個(gè)制造系統(tǒng)的術(shù)語。歷史上,它們是以晶體管的柵極長度命名的。

然而,隨著制造技術(shù)的改進(jìn),允許越來越小的組件,命名不再遵循芯片的物理方面,現(xiàn)在它只是一個(gè)營銷工具。然而,每一個(gè)新的工藝節(jié)點(diǎn)都會(huì)帶來比前者更多的好處。

它的生產(chǎn)成本可能更低,在相同的時(shí)鐘速度下消耗更少的功率(或者相反),或者具有更高的密度。后者衡量的是在一個(gè)給定的芯片區(qū)域內(nèi)可以容納多少元件。

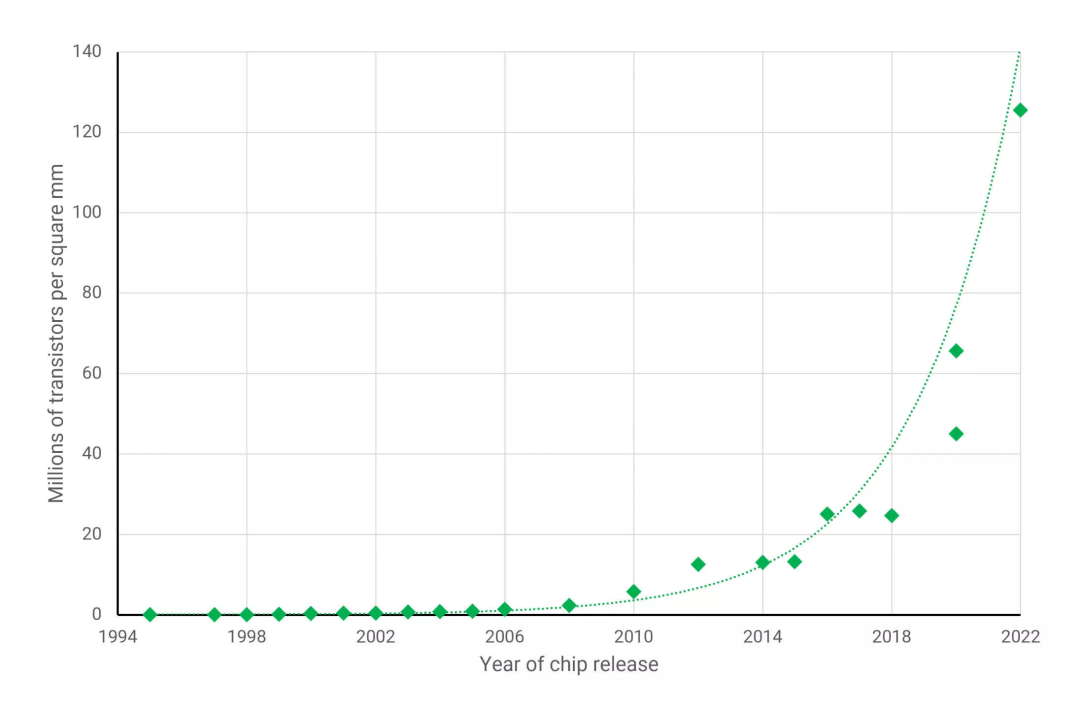

在下圖中,你可以看到這些年來GPU(你在PC中發(fā)現(xiàn)的最大和最復(fù)雜的芯片)的發(fā)展情況。

工藝節(jié)點(diǎn)的改進(jìn)為工程師提供了提高其產(chǎn)品能力和性能的手段,而不必使用大而昂貴的芯片。

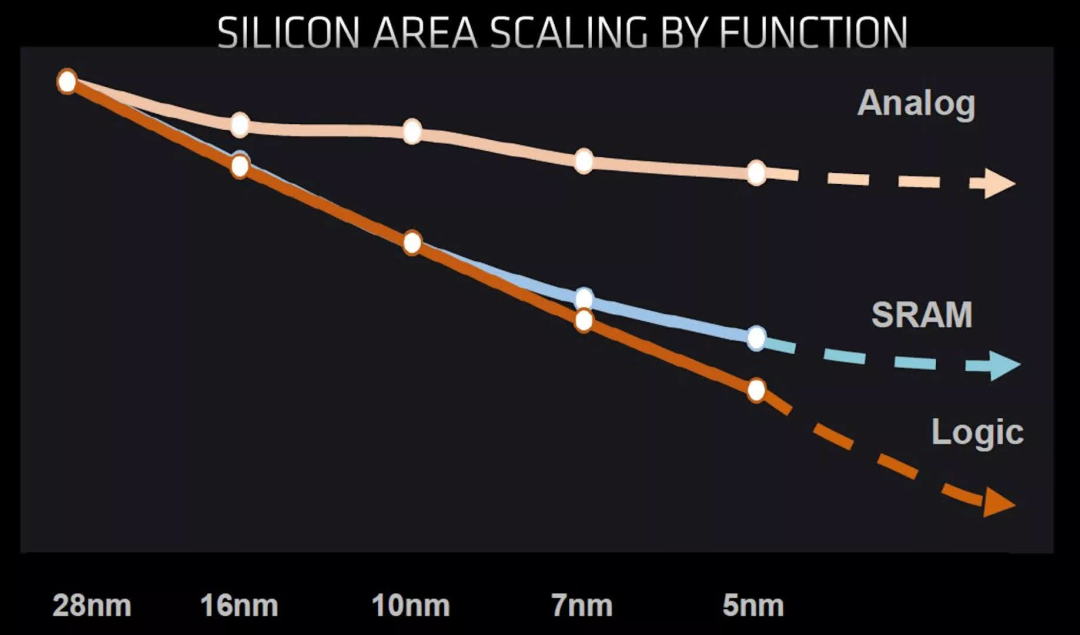

然而,上圖只說明了部分情況,因?yàn)椴皇翘幚砥鞯拿總€(gè)方面都能從這些進(jìn)步中受益。芯片內(nèi)的電路可以被分配到以下幾大類中的一類:

(1)邏輯,處理數(shù)據(jù)、數(shù)學(xué)和決策;

(2)存儲(chǔ)器,通常是SRAM,用于存儲(chǔ)邏輯的數(shù)據(jù);

(3)模擬 ,管理芯片和其他設(shè)備之間信號(hào)的電路。

當(dāng)邏輯電路隨著工藝節(jié)點(diǎn)技術(shù)的每一次重大進(jìn)步而繼續(xù)縮小時(shí),模擬電路幾乎沒有變化,SRAM也開始達(dá)到極限。

雖然邏輯仍然構(gòu)成了芯片的最大部分,但今天的CPU和GPU中的SRAM數(shù)量在近年來有了顯著增長。

例如,AMD在其Radeon VII顯卡中使用的Vega 20芯片的L1和L2緩存合計(jì)為5MB。僅僅兩代GPU之后,Navi 21就有超過130MB的各種緩存--比Vega 20多了25倍,令人矚目。

可以預(yù)期,隨著新一代處理器的開發(fā),這些水平將繼續(xù)提高,但由于存儲(chǔ)器的規(guī)模沒有像邏輯那樣縮小,在同一工藝節(jié)點(diǎn)上制造所有電路的成本效益將越來越低。

在一個(gè)理想的世界里,人們?cè)谠O(shè)計(jì)芯片時(shí),模擬部分在最大和最便宜的節(jié)點(diǎn)上制造,SRAM部分在更小的節(jié)點(diǎn)上制造,而邏輯部分則保留給絕對(duì)尖端的技術(shù)。

不幸的是,這在實(shí)踐中是無法實(shí)現(xiàn)的。然而,存在一種替代方法。

?分而治之

早在1995年,英特爾推出了其原始P5處理器的繼任者--奔騰II。它與當(dāng)時(shí)的常規(guī)產(chǎn)品不同的是,在塑料外殼下有一塊電路板,里面有兩個(gè)芯片:主芯片,包含所有的處理邏輯和模擬系統(tǒng),以及一個(gè)或兩個(gè)獨(dú)立的SRAM模塊,作為二級(jí)緩存。

英特爾公司生產(chǎn)主芯片,但緩存來自其他公司。在20世紀(jì)90年代中后期,這將成為臺(tái)式電腦的相當(dāng)標(biāo)準(zhǔn),直到半導(dǎo)體制造技術(shù)改進(jìn)到可以將邏輯、內(nèi)存和模擬全部集成到同一芯片中。

雖然英特爾繼續(xù)嘗試在同一封裝中使用多個(gè)芯片,但它在很大程度上堅(jiān)持了所謂的處理器單片(monolithic)方法(即一個(gè)芯片用于一切)。

對(duì)于大多數(shù)處理器來說,不需要超過一個(gè)芯片,因?yàn)橹圃旒夹g(shù)已經(jīng)足夠熟練(而且價(jià)格低廉),可以保持簡(jiǎn)單直接。然而,其他公司對(duì)遵循多芯片方法更感興趣,最引人注目的是IBM。2004年,IBM提供了8芯片版本的POWER4服務(wù)器CPU,它由四個(gè)處理器和四個(gè)緩存模塊組成,都安裝在同一個(gè)機(jī)身內(nèi)(稱為多芯片模塊或MCM方法)。

大約在這個(gè)時(shí)候,"異質(zhì)集成"一詞開始出現(xiàn),部分原因是DARPA(國防高級(jí)研究計(jì)劃局)所做的研究工作。異質(zhì)集成的目的是將處理系統(tǒng)的各個(gè)部分分開,在最適合每個(gè)部分的節(jié)點(diǎn)上單獨(dú)制造,然后將它們合并到同一個(gè)包中。 今天,這被稱為系統(tǒng)級(jí)封裝(SiP),從一開始就是為智能手表配備芯片的標(biāo)準(zhǔn)方法。

例如,第1代的Apple Watch在單一結(jié)構(gòu)中裝有一個(gè)CPU、一些DRAM和NAND閃存、多個(gè)控制器和其他組件。

通過將不同的系統(tǒng)全部放在單個(gè)芯片上(稱為片上系統(tǒng)或SoC),可以實(shí)現(xiàn)類似的效果。但是,這種方法不允許利用不同的節(jié)點(diǎn)價(jià)格,也不能以這種方式制造每個(gè)組件。

對(duì)于技術(shù)供應(yīng)商來說,對(duì)利基產(chǎn)品使用異構(gòu)集成是一回事,但將其用于其大部分產(chǎn)品組合則是另一回事。這正是AMD對(duì)其處理器系列所做的。2017年,這家半導(dǎo)體巨頭以單芯片Ryzen桌面CPU的形式發(fā)布了其Zen架構(gòu)。幾個(gè)月后,兩條多芯片產(chǎn)品線Threadripper和EPYC首次亮相,后者擁有多達(dá)四個(gè)芯片。

隨著兩年后Zen 2的推出,AMD完全接受了異質(zhì)集成,MCM,SiP 。他們將大部分模擬系統(tǒng)移出處理器,并將它們放入單獨(dú)的芯片中。這些是在更簡(jiǎn)單、更便宜的工藝節(jié)點(diǎn)上制造的,而更高級(jí)的流程節(jié)點(diǎn)則用于剩余的邏輯和緩存。 自此,Chiplets成為流行。

?越小越好 ?

為了準(zhǔn)確理解AMD為什么選擇這個(gè)方向,我們來看看下面的圖片。它展示了Ryzen 5系列的兩款CPU,左邊是采用所謂Zen+架構(gòu)的2600,右邊是由Zen 2驅(qū)動(dòng)的3600。兩種型號(hào)的散熱器都已被拆除,照片是用紅外相機(jī)拍攝的。2600的單芯片容納了八個(gè)核心,盡管其中兩個(gè)核心在這個(gè)特定的模型中被禁用。

這也是3600的情況,但在這里我們可以看到,封裝中有兩個(gè)模具--頂部的Core Complex Die(CCD),容納了核心和緩存,底部的Input/Output Die(IOD)包含所有控制器(用于內(nèi)存、PCI Express、USB等)和物理接口。 由于這兩顆Ryzen CPU都適用于同一個(gè)主板插座,這兩張圖片基本上是按比例繪制的。

從表面上看,3600的兩個(gè)芯片似乎比2600的單個(gè)芯片有更大的綜合面積,但外表可能是欺騙性的。 如果我們直接比較包含核心的芯片,很明顯可以看到舊型號(hào)中模擬電路所占用的空間(圍繞著金色的核心和緩存的藍(lán)綠顏色)。然而,在Zen 2 CCD中,用于模擬系統(tǒng)的芯片面積很少;它幾乎完全由邏輯和SRAM組成。

Zen+芯片的面積為213平方毫米,由GlobalFoundries使用其12納米工藝節(jié)點(diǎn)制造。對(duì)于Zen 2,AMD保留了GlobalFoundries對(duì)125平方毫米IOD的服務(wù),但在73平方毫米的CCD上使用了臺(tái)積電的N7節(jié)點(diǎn)。

Zen+ (上)vs Zen 2 CCD (下) 較新型號(hào)的芯片的綜合面積更小,而且它還擁有兩倍的L3緩存,支持更快的內(nèi)存和PCI Express。然而,Chiplets方法最好的部分是,CCD的緊湊尺寸使AMD有可能將另一個(gè)CCD裝入包裝。這一發(fā)展催生了Ryzen 9系列,為臺(tái)式電腦提供12和16核型號(hào)。更重要的是,通過使用兩個(gè)較小的芯片而不是一個(gè)大的芯片,每個(gè)晶圓可能會(huì)產(chǎn)生更多的芯片。

就Zen 2 CCD而言,一塊12英寸(300毫米)的晶圓可以比Zen+型號(hào)多生產(chǎn)85%的芯片。 從晶圓上取下的切片越小,就越不可能發(fā)現(xiàn)制造缺陷(因?yàn)樗鼈兺请S機(jī)分布在光盤上的),所以考慮到所有這些,Chiplets不僅使AMD有能力擴(kuò)大其產(chǎn)品組合,而且成本效益更高。相同的CCD可用于多個(gè)型號(hào),每個(gè)晶圓可生產(chǎn)數(shù)百個(gè)。 但是,如果這種設(shè)計(jì)選擇如此有優(yōu)勢(shì),為什么英特爾不這樣做呢?為什么我們沒有看到它被用于其他處理器,如GPU?

?跟隨潮流

為了解決第一個(gè)問題,英特爾確實(shí)在采用全芯片路線,而且它的下一個(gè)消費(fèi)者CPU架構(gòu)(Meteor Lake)也將這樣做。英特爾的方法有些獨(dú)特,讓我們來看看它與AMD的方法有何不同。 這一代處理器使用 "區(qū)塊(tile)"一詞而不是 "芯片",將以前的單片式設(shè)計(jì)分割成四個(gè)獨(dú)立的芯片:(1)計(jì)算區(qū)塊:包含所有的內(nèi)核和二級(jí)緩存;(2)GFX區(qū)塊:容納集成GPU;(3)SOC區(qū)塊:整合了L3高速緩存、PCI Express和其他控制器;(4)IO區(qū)塊:容納內(nèi)存和其他設(shè)備的物理接口。

在SOC和其他三個(gè)區(qū)塊之間存在高速、低延遲的連接,并且所有這些區(qū)塊都與另一個(gè)被稱為插板的芯片相連。這個(gè)插板為每個(gè)芯片提供電源,并包含它們之間的導(dǎo)線。然后,插板和四塊區(qū)塊被安裝到另一塊板上,以便將整個(gè)組件封裝起來。

與英特爾不同,AMD不使用任何特殊的安裝模具,而是有自己獨(dú)特的連接系統(tǒng),被稱為Infinity Fabric,以處理芯片數(shù)據(jù)交易。電源傳輸通過一個(gè)相當(dāng)標(biāo)準(zhǔn)的封裝運(yùn)行,而且AMD還使用較少的芯片。那么,為什么英特爾的設(shè)計(jì)是這樣的呢? AMD的方法的一個(gè)挑戰(zhàn)是,它不太適合超移動(dòng)、低功耗領(lǐng)域。

這就是為什么AMD在該領(lǐng)域仍然使用單片式CPU。英特爾的設(shè)計(jì)允許他們混合和匹配不同的區(qū)塊以滿足特定的需求。例如,經(jīng)濟(jì)型筆記本電腦的預(yù)算型號(hào)可以到處使用小得多的芯片,而AMD只有一種尺寸的芯片用于每種用途。 英特爾系統(tǒng)的缺點(diǎn)是生產(chǎn)復(fù)雜且昂貴,盡管現(xiàn)在預(yù)測(cè)這將如何影響零售價(jià)格還為時(shí)尚早。然而,兩家CPU公司都完全致力于芯片的概念。一旦制造鏈的每一部分都圍繞它進(jìn)行設(shè)計(jì),成本就會(huì)降低。

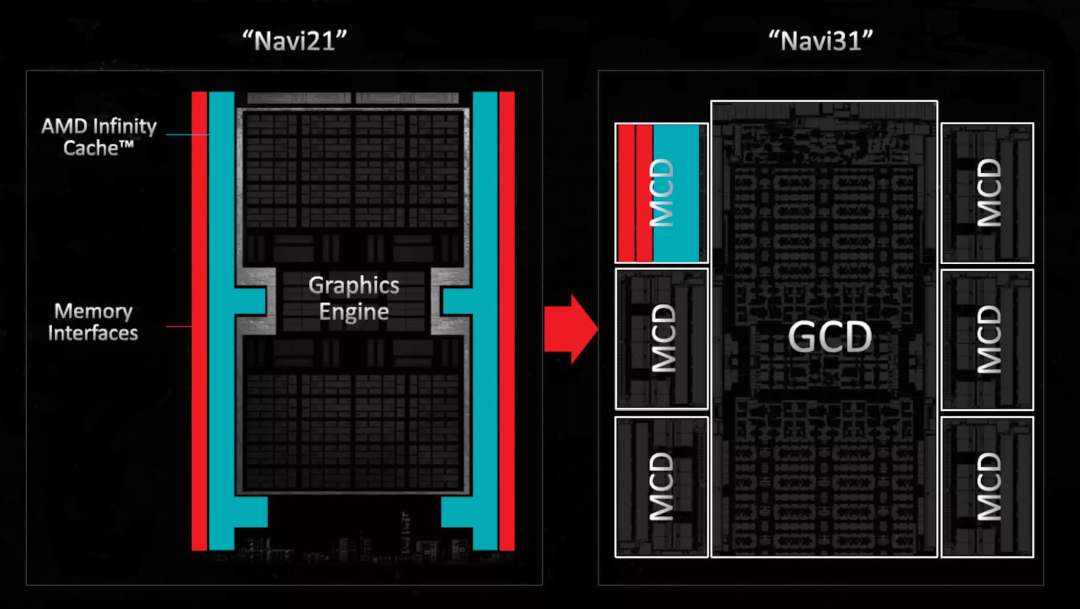

關(guān)于GPU,與芯片的其他部分相比,它們包含的模擬電路相對(duì)較少,但里面的SRAM數(shù)量正在穩(wěn)步增加。

這就是為什么AMD將其芯片知識(shí)應(yīng)用于其最新的Radeon 7000系列,Radeon RX 7900 GPU包括多個(gè)芯片--一個(gè)用于核心和二級(jí)緩存的大芯片,以及五六個(gè)Chiplets,每個(gè)芯片包含一片L3緩存和一個(gè)內(nèi)存控制器。

通過將這些部件移出主芯片,工程師們能夠大大增加邏輯數(shù)量,而不需要使用最新的工藝節(jié)點(diǎn)來控制芯片尺寸。然而,這一變化并沒有增強(qiáng)圖形組合的廣度,盡管它可能確實(shí)有助于改善整體成本。

目前,英特爾和英偉達(dá)在其GPU設(shè)計(jì)方面沒有顯示出跟隨AMD的跡象。

兩家公司都使用臺(tái)積電承擔(dān)所有的制造任務(wù),似乎滿足于生產(chǎn)極其龐大的芯片,將成本轉(zhuǎn)嫁給消費(fèi)者。

隨著圖形領(lǐng)域的收入穩(wěn)步下降,可能會(huì)在未來幾年內(nèi)看到每個(gè)GPU供應(yīng)商都采用同樣的路線。

用Chiplets實(shí)現(xiàn)摩爾定律

盡管在半導(dǎo)體制造方面取得了巨大的技術(shù)進(jìn)步,但每個(gè)部件可以縮小的程度是有明確限制的。為了繼續(xù)提高芯片的性能,工程師們基本上有兩個(gè)途徑:增加更多的邏輯,用必要的內(nèi)存來支持它,以及提高內(nèi)部時(shí)鐘速度。關(guān)于后者,一般的CPU在這方面已經(jīng)多年沒有明顯的變化了。

AMD的FX-9590處理器,從2013年開始,在某些工作負(fù)載中可以達(dá)到5GHz,而其當(dāng)前型號(hào)的最高時(shí)鐘速度是5.7GHz(Ryzen 9 7950X)。

英特爾最近推出了酷睿i9-13900KS,在合適的條件下能夠達(dá)到6GHz,但其大多數(shù)型號(hào)的時(shí)鐘速度與AMD的相近。 然而,改變的是電路和SRAM的數(shù)量。前面提到的FX-9590有8個(gè)核心(和8個(gè)線程)和8MB的L3緩存,而7950X3D擁有16個(gè)核心、32個(gè)線程和128MB的L3緩存。

英特爾的CPU在核心和SRAM方面也有類似的擴(kuò)展。 Nvidia的第一個(gè)統(tǒng)一著色器GPU,即2006年的G80,由6.81億個(gè)晶體管、128個(gè)內(nèi)核和96 kB的二級(jí)緩存組成,其芯片面積為484 mm2。快進(jìn)到2022年,當(dāng)AD102推出時(shí),它現(xiàn)在由763億個(gè)晶體管、18432個(gè)內(nèi)核和98304 kB的二級(jí)緩存組成,芯片面積為608 mm2。

1965年,飛兆半導(dǎo)體公司的聯(lián)合創(chuàng)始人戈登·摩爾(Gordon Moore)觀察到,在芯片制造的早期,在固定的最低生產(chǎn)成本下,芯片內(nèi)的元件密度每年都在翻番。這一觀察被稱為摩爾定律,后來根據(jù)制造趨勢(shì),被解釋為 "芯片中的晶體管數(shù)量每兩年翻一番"。

近六十年來,摩爾定律一直是對(duì)半導(dǎo)體行業(yè)發(fā)展進(jìn)程的合理準(zhǔn)確描述。CPU和GPU在邏輯和內(nèi)存方面的巨大進(jìn)步是通過工藝節(jié)點(diǎn)的不斷改進(jìn)實(shí)現(xiàn)的,這些年來,組件變得越來越小。然而,這種趨勢(shì)不可能永遠(yuǎn)持續(xù)下去,無論出現(xiàn)什么新技術(shù)。

像AMD和英特爾這樣的公司并沒有等待這個(gè)極限的到來,而是轉(zhuǎn)向了Chiplets,探索它們的各種組合方式,以繼續(xù)在創(chuàng)造更強(qiáng)大的處理器方面取得進(jìn)展。

幾十年后的今天,普通的個(gè)人電腦可能是由手掌大小的CPU和GPU組成的,但是剝開散熱片,你會(huì)發(fā)現(xiàn)有許多微小的芯片--不是三四個(gè),而是幾十個(gè),都巧妙地拼接和堆疊在一起。

Chiplets的主導(dǎo)地位才剛剛開始。?

審核編輯:劉清

為什么Chiplets對(duì)處理器的未來如此重要?

- 處理器(221451)

- 模擬電路(101704)

- 存儲(chǔ)器(161620)

- gpu(126253)

- SRAM芯片(11937)

相關(guān)推薦

手機(jī)廠商為何對(duì)研發(fā)處理器如此執(zhí)著

除了華為,聯(lián)想、陸陸續(xù)續(xù)有其他手機(jī)廠商也都有傳出在自主研發(fā)處理器的新聞,相信從2016年開始國產(chǎn)手機(jī)處理器將會(huì)爆發(fā)。那在處理器市場(chǎng)洗牌穩(wěn)定已久之時(shí),為何又有廠商對(duì)自主研發(fā)處理器如此執(zhí)著呢?

2015-10-13 08:37:27 760

760

760

76032位嵌入式處理器的市場(chǎng)

嵌入式系統(tǒng)以各種類型的嵌入式處理器為核心,而隨著技術(shù)的發(fā)展,對(duì)于嵌入式處理器的性能及功耗的要求愈加嚴(yán)苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場(chǎng)已逐步趨向穩(wěn)定

2019-07-19 08:29:10

處理器的電源管理原理

處理器的電源管理原理 預(yù)測(cè)到2010年,處理器將工作在1V和100A電流,到2020年希望處理器

2009-10-22 17:10:37

ADI SHARC處理器有哪些應(yīng)用案例

SHARC?處理器系列在浮點(diǎn)DSP市場(chǎng)占據(jù)主導(dǎo)地位,擁有出色的內(nèi)核和存儲(chǔ)器性能以及優(yōu)異的I/O吞吐能力。SHARC處理器將浮點(diǎn)處理性能帶給動(dòng)態(tài)范圍至關(guān)重要的應(yīng)用,性價(jià)比高達(dá)319 MFLOPS/美元

2018-10-31 09:21:14

ARM Cortex系列處理器知識(shí)點(diǎn)匯總

ARM Cortex系列處理器――Cortex-AARM Cortex系列處理器——Cortex-MARM Cortex系列處理器——Cortex-R

2021-01-12 07:54:17

ARM cortex 處理器本身仿真要注意什么

ARM cortex 處理器本身仿真要注意什么,uvm仿真時(shí)處理器本身arm提供驗(yàn)證list嗎?

2022-08-05 14:14:40

ARM處理器及ARM處理器工作模式

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時(shí)處理器執(zhí)行32位的字對(duì)齊的ARM指令;第二種為Thumb狀態(tài),此時(shí)處理器執(zhí)行16位的、半字對(duì)齊

2011-01-27 11:13:20

ARM處理器及ARM處理器工作模式

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時(shí)處理器執(zhí)行32位的字對(duì)齊的ARM指令;第二種為Thumb狀態(tài),此時(shí)處理器執(zhí)行16位的、半字對(duì)齊

2011-01-27 14:19:05

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論