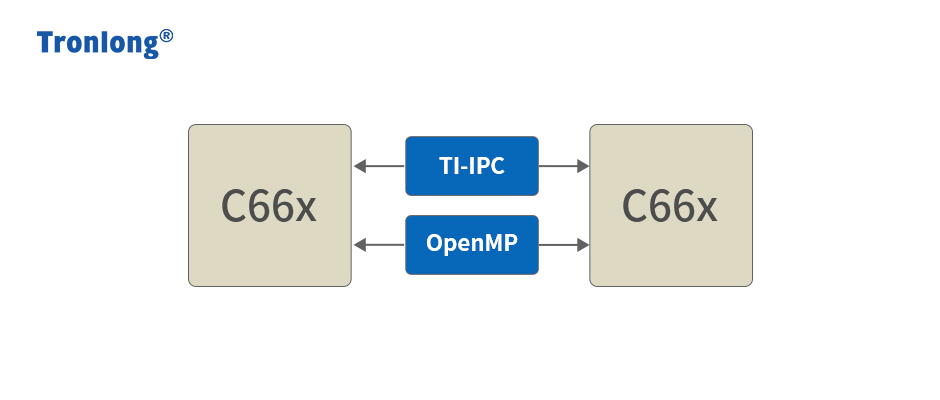

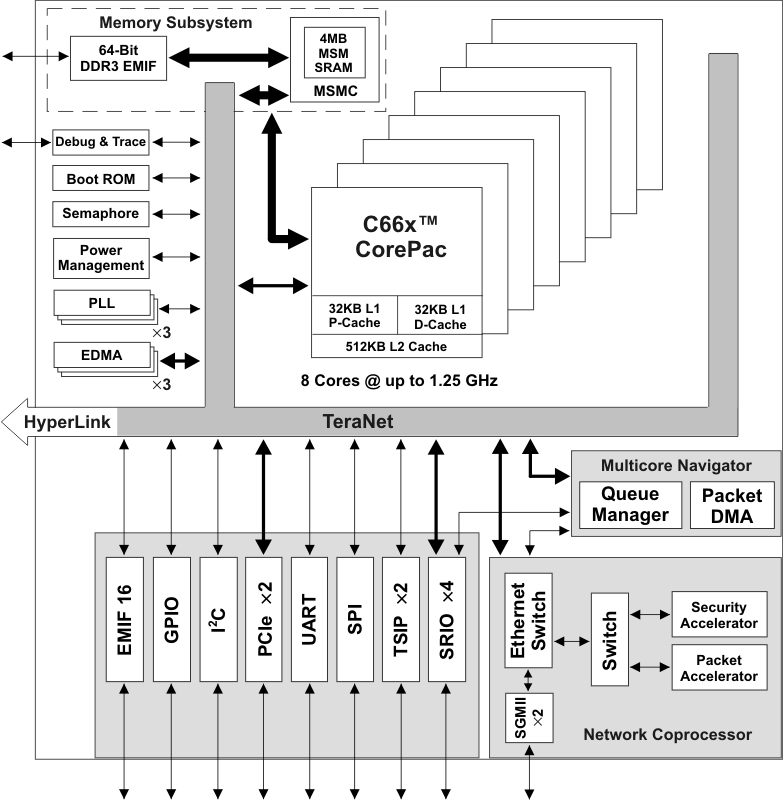

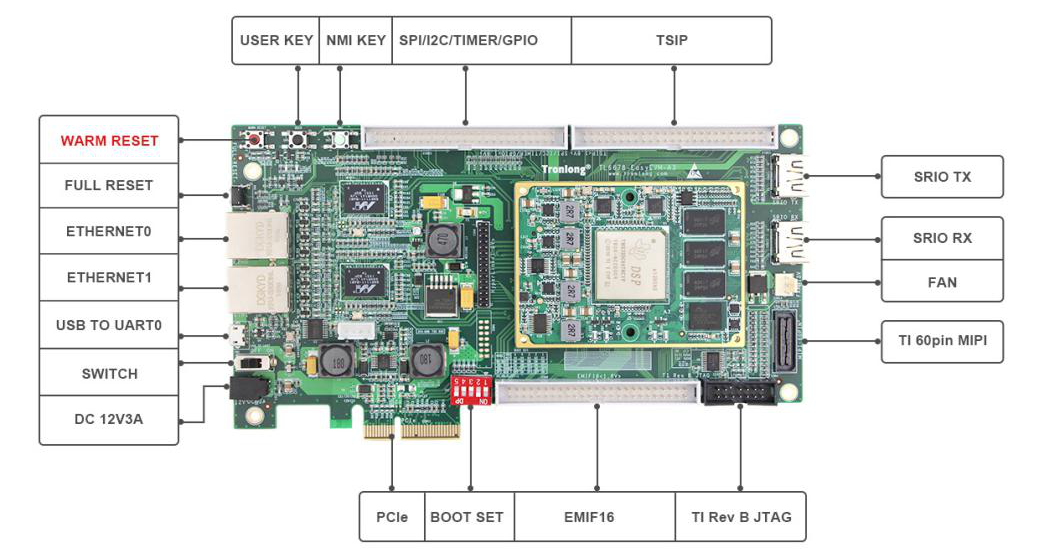

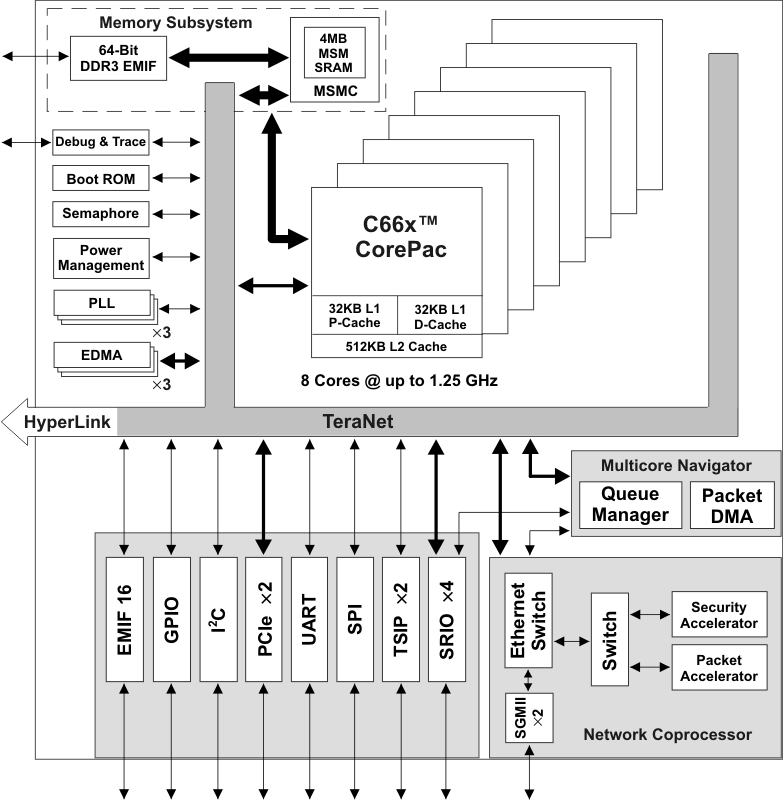

前言 ? ?? ???嵌入式領域的處理器已向多核架構迅速發展,ti公司的KeyStone架構的TMS320C6678是目前市面上性能最高的多核DSP處理器。TMS320C6678集成8核C66x DSP處理器,每個內核頻率高達1.25 GHz,提供每秒高達40 GMAC定點運算和20 GFLOP浮點運算能力;1片TMS320C6678提供等效達10 GHz的內核頻率,單精度浮點并行運算能力理論上可達160 GFLOP,是TS201S的50倍、C67x+的115.2倍,適合于諸如油氣勘探、雷達信號處理、圖像處理以及定位導航等對定浮點運算能力及實時性有較高要求的超高性能計算應用。  ? ?? ???然而,核間通信是多核處理器系統所面臨的主要難點,通信機制的優劣直接影響多核處理器的性能,高效的通信機制是發揮多核處理器高性能的重要保障。 ? ?? ???創龍科技(Tronlong)專注于DSP、ARM、FPGA多核異構技術開發,本文為您介紹TMS320C6678處理器開發中比較常用的兩種多核通信方式:TI-IPC和OpenMP,以及多核編程注意事項。 1 硬件平臺 ? ?? ???本文基于創龍科技TL6678-EasyEVM評估板進行演示。 ? ?? ???TL6678-EasyEVM是一款基于TI KeyStone架構c6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP評估板,由核心板與底板組成。核心板經過專業的PCB?Layout和高低溫測試驗證,穩定可靠,可滿足各種工業應用環境。 ? ?? ???評估板接口資源豐富,引出雙路千兆網口、SRIO、PCIe等高速通信接口,方便用戶快速進行產品方案評估與技術預研。

?

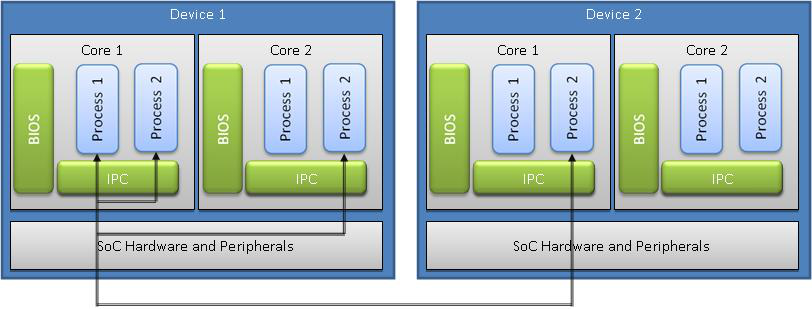

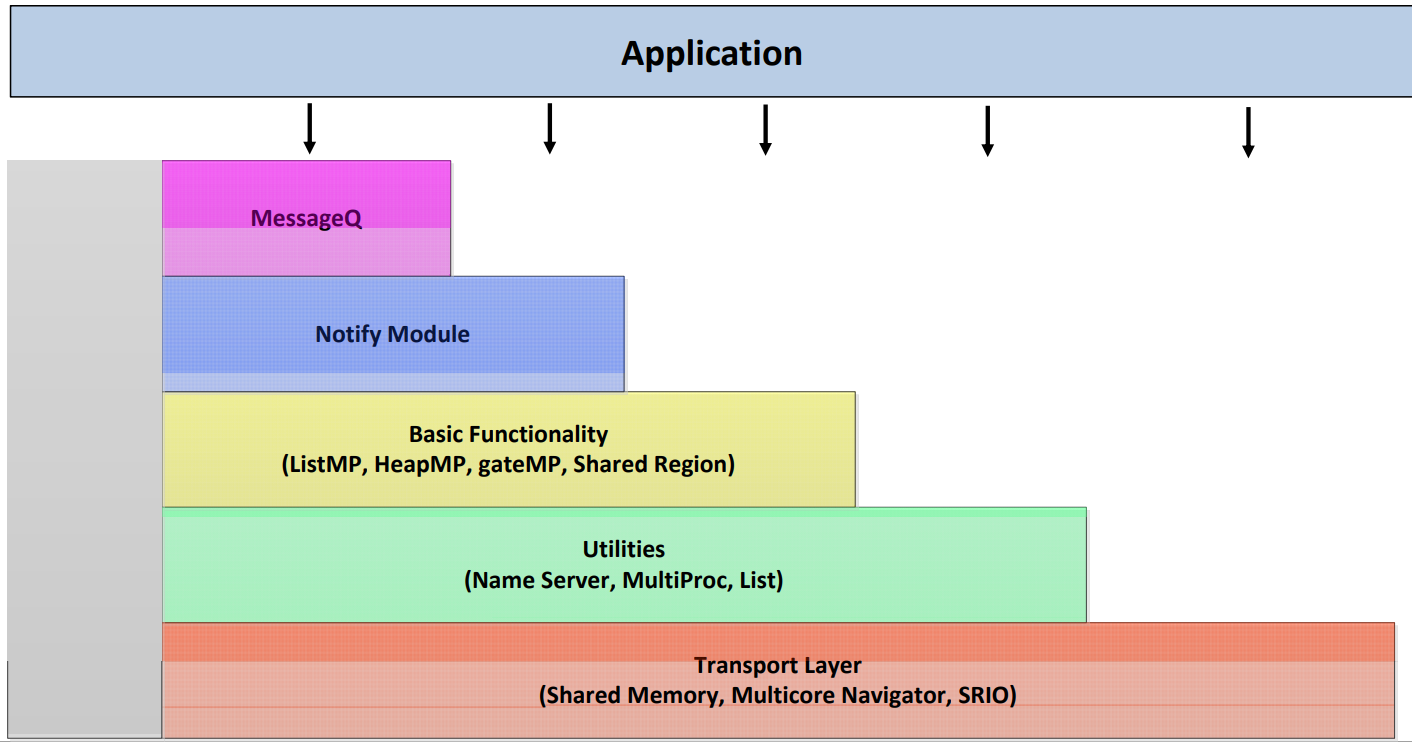

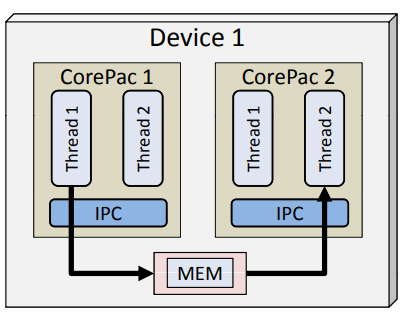

TL6678-EasyEVM評估板 開發案例主要包括: (1) 裸機開發案例 (2) RTOS(SYS/BIOS)開發案例 (3) IPC、OpenMP多核開發案例 (4) SRIO、PCIe、雙千兆網口開發案例 (5) 圖像處理開發案例 (6) DSP算法開發案例 (7) 串口、網絡遠程升級開發案例 C66x DSP視頻教程、中文手冊、產品資料(用戶手冊、核心板硬件資料、產品規格書)可點:site.tronlong.com/pfdownload 直接獲取。 2 TI-IPC 2.1 簡介 ? ?? ???TI-IPC(Inter-Processor Communication)組件提供與處理器硬件無關的API,可用于多核處理器核間通信、同一處理器進程間通信和設備間通信。API支持消息傳遞、流和鏈接列表,它們在單處理器和多處理器中配置均可兼容。 ? ?? ???TI-IPC被設計在運行SYS/BIOS應用程序的處理器上使用,一般為DSP處理器(如TMS320C6678、TMS320C6657),但在某些情況下亦可能是ARM處理器。

?

IPC常見的通信模塊如下: 表1

?

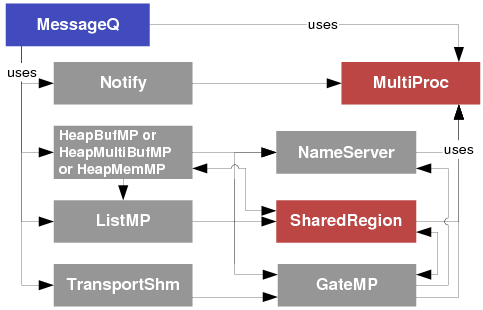

2.2 常用模塊 2.2.1 MessageQ 該模塊具有如下特點: (1) 兼容性強,可在不更改運行代碼的情況移植至另一個支持TI-IPC MessageQ的處理器或其他傳輸層(如Shared Memory、Multicore Navigator、SRIO)。 (2) 支持可變長度消息的結構化發送與接收。 (3) 單個MessageQ隊列支持單個reader和多個writer。 (4) 消息接收支持超時機制。 (5) reader可根據消息頭部信息對writer進行確認后再回復。 (6) Ipc_start()會幫助用戶完成下圖中灰色框內的功能,用戶僅需關注紅色框中的內容即可。

?

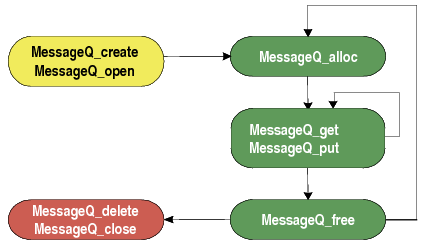

? ?? ???MessageQ通過消息隊列發送和接收消息。reader是一個從消息隊列中讀取消息的線程,writer是一個將消息寫入消息隊列的線程。每個消息隊列都有一個reader,但可有多個writer。 ■ reader:調用MessageQ_create()、MessageQ_get()、MessageQ_free()和MessageQ_delete()。 ■ writer:調用MessageQ_open()、MessageQ_alloc()、MessageQ_put()和MessageQ_close()。 ? ?? ???MessageQ常見的工作流程如下所示。

?

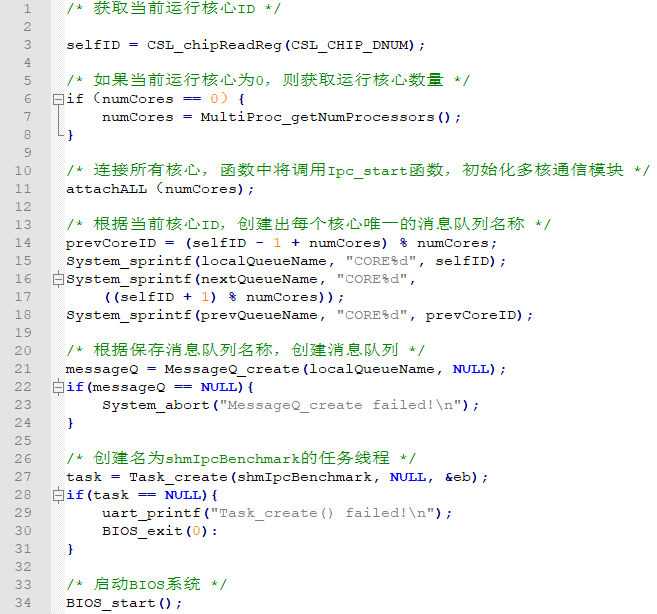

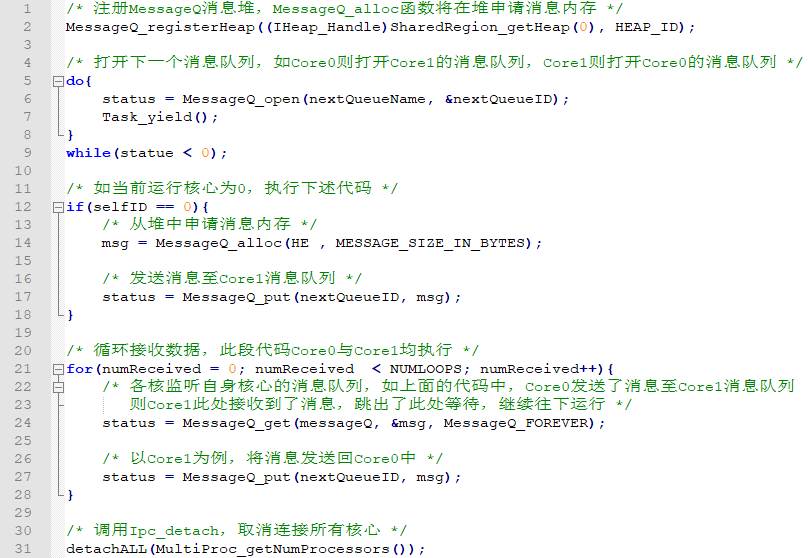

? ?? ???下面以多核IPC通信的shmIpcBenchmark案例為例,分析代碼中MessageQ的使用,見圖中注釋。

?

?

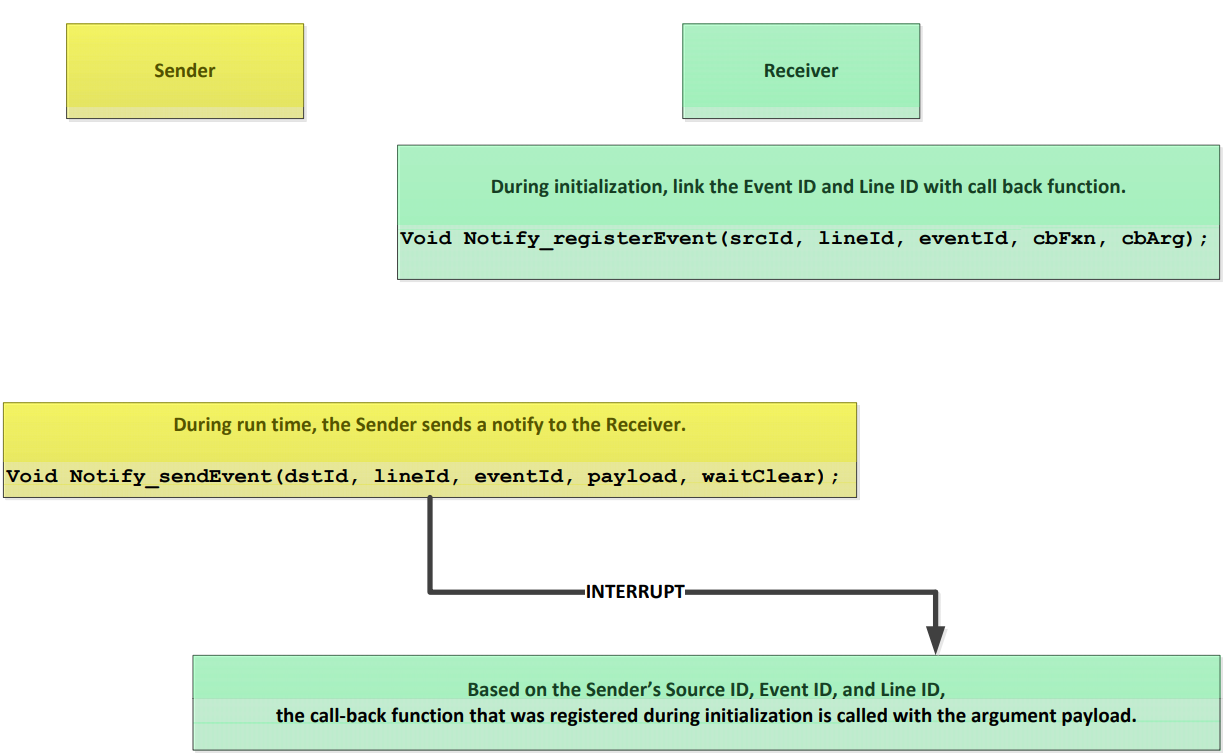

2.2.2 Notify 該模塊具有如下特點: (1) 可獨立于MessageQ模塊進行使用。 (2) 著重于多核通知功能,是更為簡單的多核通信形式。

?

(3) 僅可基于Shared Memroy方式進行使用。

?

? ?? ?Notify通過硬件中斷傳輸消息,Receiver注冊Notify事件中斷,Sender通過Notify發送事件中斷,從而實現通知并攜帶小量消息的目的。 ■ Receiver:調用Notify_registerEvent()注冊事件中斷服務函數。 ■ Sender:調用Notify_sendEvent()發送事件中斷。 ? ?? ?Notify常見的工作流程如下所示。

?

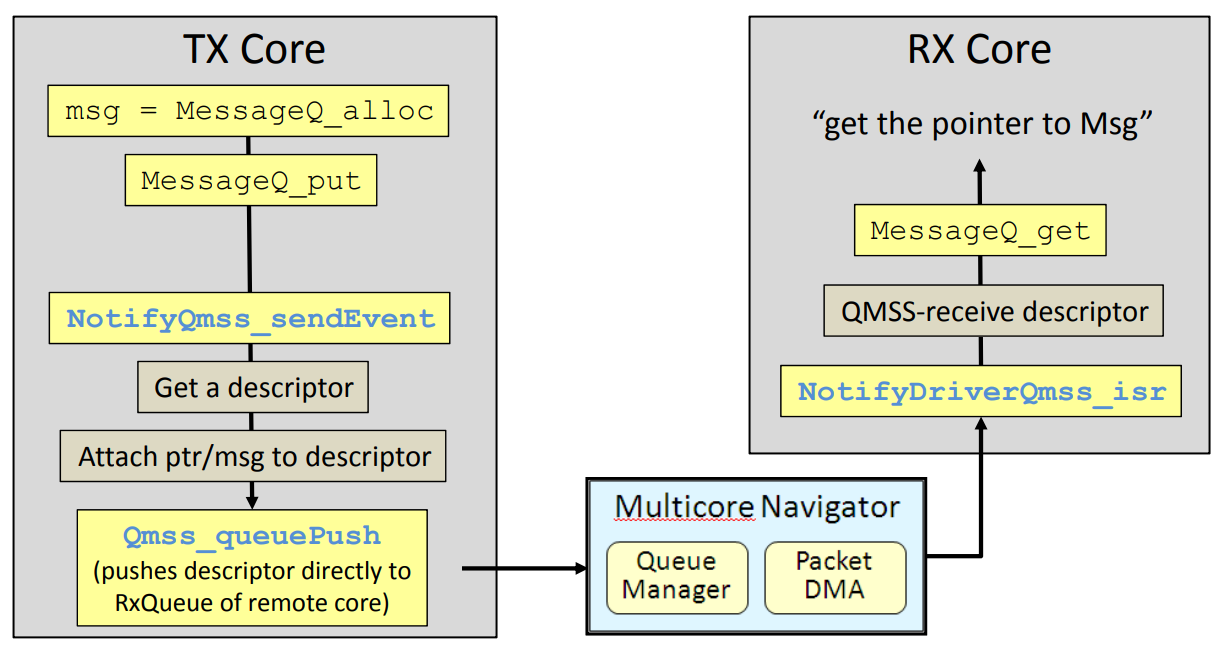

2.3 物理傳輸方式 ? ?? ?TI-IPC的數據傳輸需結合特定物理硬件與底層驅動,方可實現兩個線程在同一個設備或跨設備間進行通信。常用三種的物理傳輸方式包括Shared Memory、Multicore Navigator和SRIO,具體說明如下。 表2

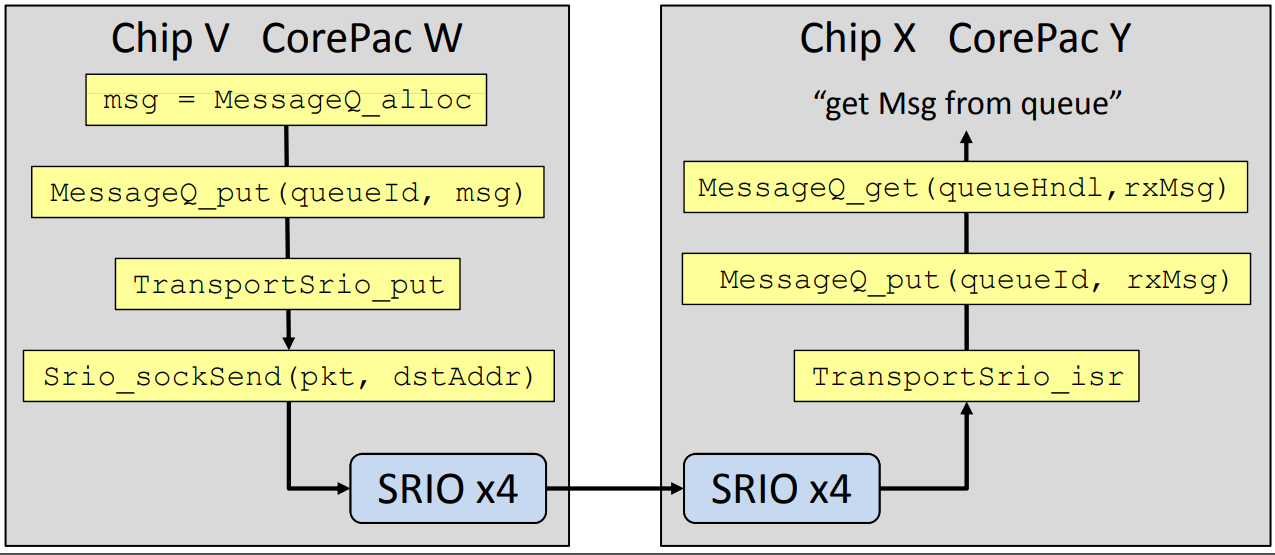

? ?? ?下圖為使用Multicore Navigator、SRIO的API調用流程,用戶僅需關注MessageQ部分操作即可,其他模塊均由系統自動調用。

?

?

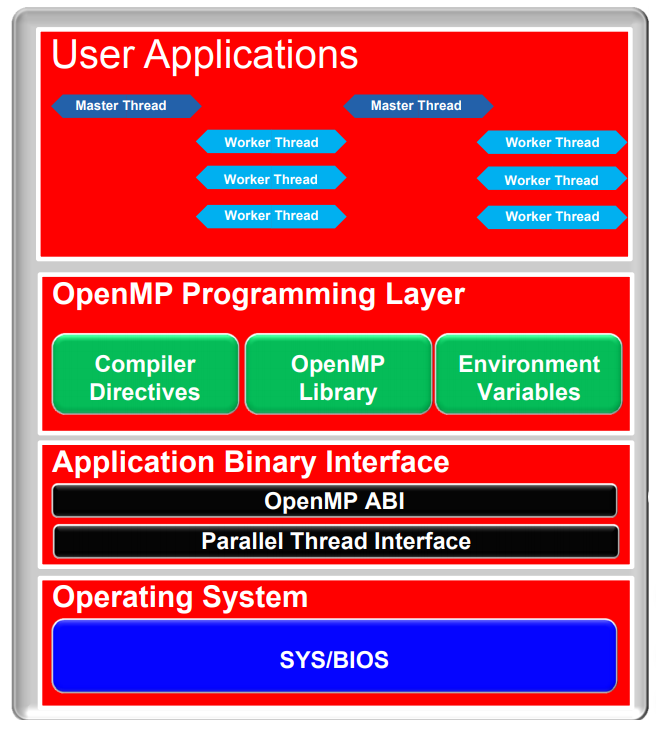

3 OpenMP 3.1 簡介OpenMP是一種多核開發軟件框架,其主要特性如下: (1) 可跨平臺使用,代碼兼容性強。 (2) 以共享內存為通信基礎。 (3) 支持C/C++以及Fortran語言。 (4) 一般基于SYS/BIOS運行。

?

3.2 基本語法 #pragma omp?指令?[子句 [ [ [,]子句 ] ... ] { ... } ? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ???表3

? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?表4

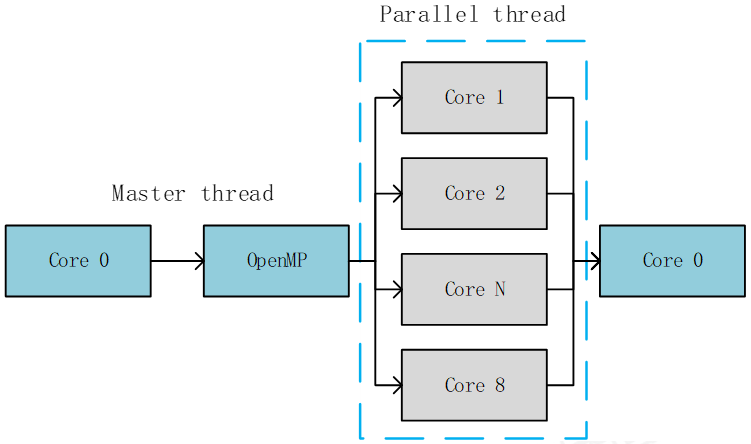

? ?? ?以裸機的omp_matavec案例為例,使用場景的概要流程圖如下。 ? ?? ?C66xx_0核心創建主線程,通過OpenMP框架加載matvec算法至C66xx_0~C66xx_7核心進行并行運算,從而減少C66xx_0核心負載,并可加快運算速度。

?

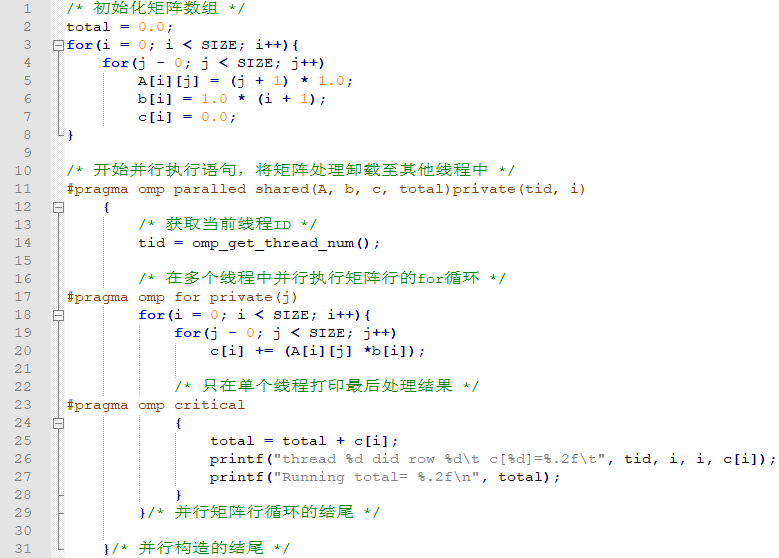

3.3 代碼分析 ? ?? ?以裸機的omp_matavec案例為例進行代碼分析,見圖中注釋。

?

4 多核編程注意事項 4.1 多核單/多鏡像 ? ?? ?在開發過程中,需將程序可執行文件分別加載至對應的核心運行。此時需了解多核單/多鏡像的優缺點,再根據實際情況進行選擇。 多核單鏡像 多核單鏡像指所有核心運行完全相同的用戶程序。 優點:僅需維護一個工程,管理便捷。 缺點:需兼容多個核心代碼,程序可執行文件較大。 多核多鏡像 多核多鏡像指不同核心運行不同的用戶程序。 優點:無需考慮各核心功能的兼容性,單個程序可執行文件較小。 缺點:需維護多個工程,管理不便。 4.2 外設訪問 ? ?? ?所有核心共享外設,如SRIO、PCIe、Ethernet、SPI、I2C、EMIF等。在對外設進行初始化后,所有核心可在任意時間對外設進行讀寫,無需再次初始化。

?

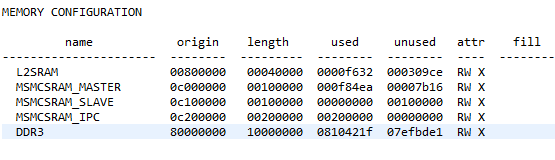

4.3 數據存儲 (1) 注意區分全局與局部地址。 ? ?? ?L1/L2SRAM有全局與局部兩個地址,全局地址可被所有核心訪問,但局部地址僅可被指定核心訪問。 ? ?? ?以C66xx_0核心的L2SRAM為例,對應的全局地址為0x10800000,局部地址為0x00800000。C66xx_0核心使用0x10800000或0x00800000,均可訪問C66xx_0核心的L2SRAM。而C66xx_1核心使用0x00800000僅可訪問C66xx_1核心的L2SRAM,使用0x10800000方可訪問C66xx_0核心的L2SRAM。 ? ?? ?L2SRAM全局與局部地址對應關系如下表: ? ?? ?? ?? ?? ?? ?? ???表5

(2)注意避免內存沖突。 如數據需存放至MSMCSRAM、ddr3共享內存設備,請將對應內存劃分為MSMCSRAM_MASTER段(主核使用)與MSMCSRAM_SLAVE段(從核使用),從而避免運行時內存沖突。

?

5 參考鏈接 -IPC https://training.ti.com/system/files/docs/keystone-intro-ipc-slides.pdf http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#ti-sdo-ipc-package http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#gatemp-support-for-uio-and-misc-driver http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#ti-sdo-utils-package https://processors.wiki.ti.com/index.php/IPC_Users_Guide/MessageQ_Module -OpenMP http://processors.wiki.ti.com/index.php/OpenMP_on_C6000 https://processors.wiki.ti.com/index.php/BIOS_MCSDK_2.0_User_Guide#OpenMP http://community.topcoder.com/tc?module=Static&d1=features&d2=091106 -Multicore Programming Guide https://www.ti.com/lit/an/sprab27b/sprab27b.pdf |

TMS320C6678無法連接?看看多核通信方式TI-IPC和OpenMP多核編程

- 處理器(221450)

- dsp(343833)

- 嵌入式(286111)

- TMS320C6678(17983)

- OpenMP(5583)

相關推薦

基于TMS320C6678的多核DSP上電加載技術

對于多核DSP應用技術來說,BootLoad技術是一個關鍵點,也是應用難點之一。針對8核高性能DSP——TMS320C6678的根配置問題進行了研究,包括上電加載過程,單核和多核的emif

2014-03-26 11:14:32 9494

9494

9494

949418-基于雙TMS320C6678 DSP的3U VPX的信號處理平臺

一、板卡概述 板卡由我公司自主研發,基于3U VPX架構,處理板包含兩片TI DSP TMS320C6678芯片;一片Xilinx公司的Spartan XC3S200AN 配置芯片;一片 IDT

2015-09-22 16:09:34

18-基于雙TMS320C6678 DSP的3U VPX的信號處理平臺

基于雙TMS320C6678 DSP的3U VPX的信號處理平臺一、板卡概述 板卡由我公司自主研發,基于3U VPX架構,處理板包含兩片TI DSP TMS320C6678芯片;一片Xilinx

2015-05-15 17:34:08

1創龍 C6678八核DSP核心板

1 核心板簡介? 處理器架構先進:基于TI KeyStone C66x多核定點/浮點TMS320C6678 DSP,集成了8個C66x核,支持高性能信號處理應用;? 運算能力強:每核心主頻1.0G

2016-03-30 15:38:59

246-基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡

`基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-17 14:38:59

246-基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡

基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-11 16:55:46

6-基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-05-11 17:14:29

6-基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-14 11:56:15

6-基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-18 15:24:37

6678 多核軟件仿真Illegal opcode,請問出現這個warning的原因?

您好,我的編程環境是CCSV5,使用6678多核開發板,程序主要功能是core0向其余七個核置IPC中斷,core1~core7在ISR中執行調用不同的程序或者執行不同的代碼。程序仿真過程中

2018-08-03 07:20:14

C6678 openMP 例程 連接出錯

用的芯片是c6678,開發板是TMDSEVM6678L,開發環境ccs5.2。mcsdk2.1.2.5。openMP1.1.3.02

跑的是biosMulticore sdk 中的openMP例程

2018-06-21 00:52:01

C6678 多核 IPC通信控制問題

我們使用C6678 core0作為數據接收與控制核,其每接收64M數據后,通過IPC啟動core1,2,3,4分別對16M數據進行并行處理,

在core1,2,3,4完成各自處理后分別向core0

2018-06-21 13:17:13

電子發燒友App

電子發燒友App

評論