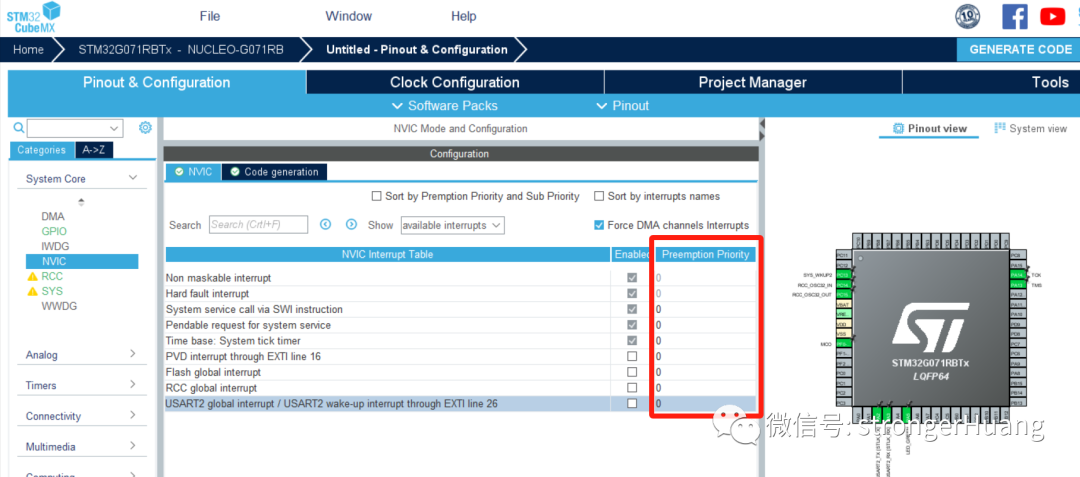

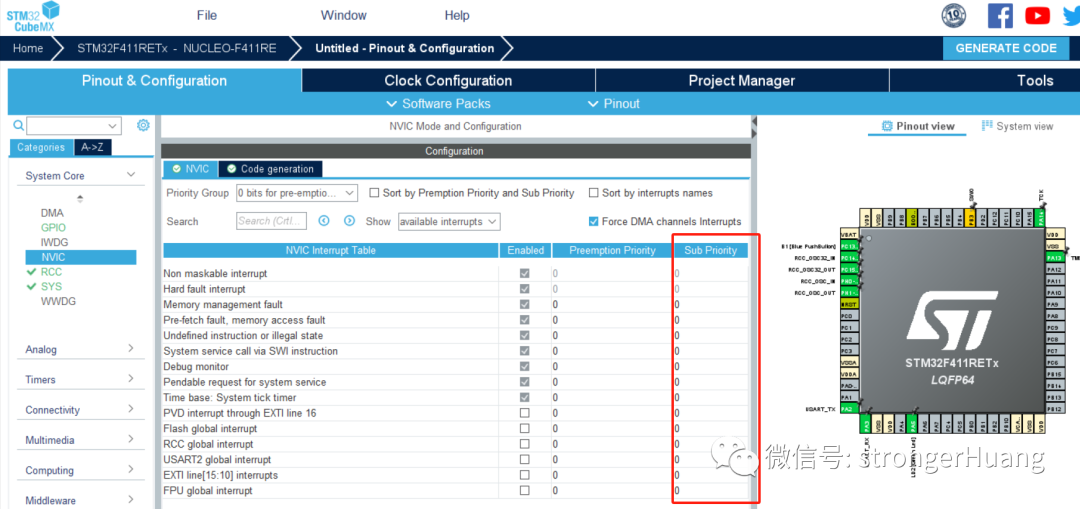

看到一個交流群在討論關于【關于STM32中斷優先級的話題】,其中就有小伙伴提到:為什么有些STM32中斷沒有【子優先級】? 比如,有時候你在使用STM32CubeMX配置時,你會發現只有Preemption Priority【搶占優先級】,而沒有Sub Priority【次優先級】:

這個問題就牽涉到STM32,準確的來說的是 Cortex-M NVIC嵌套向量中斷控制器的問題。

關于Cortex-M的NVIC

NVIC:Nested Vectored Interrupt Controller,嵌套向量中斷控制器。 在每個Cortex-M內核中都有這么一個NVIC嵌套向量中斷控制器,當MCU使用的內核不同,其中的NVIC也可能不同。 比如,Cortex-M0和Cortex-M3內核中NVIC功能就不同。 其中,中斷優先級分組功能就不同。 Cortex-M0的NVIC沒有優先級分組功能,Cortex-M3、 M4、M7有分組功能。 ?所以,你在使用STM32CubeMX配置時,M0/M0+內核的STM32是沒有【次優先級】那個選項的。

Cortex-M0包含STM32F0、L0、G0等處理器。

對底層感興趣的朋友可以繼續往下看。

?所以,你在使用STM32CubeMX配置時,M0/M0+內核的STM32是沒有【次優先級】那個選項的。

Cortex-M0包含STM32F0、L0、G0等處理器。

對底層感興趣的朋友可以繼續往下看。

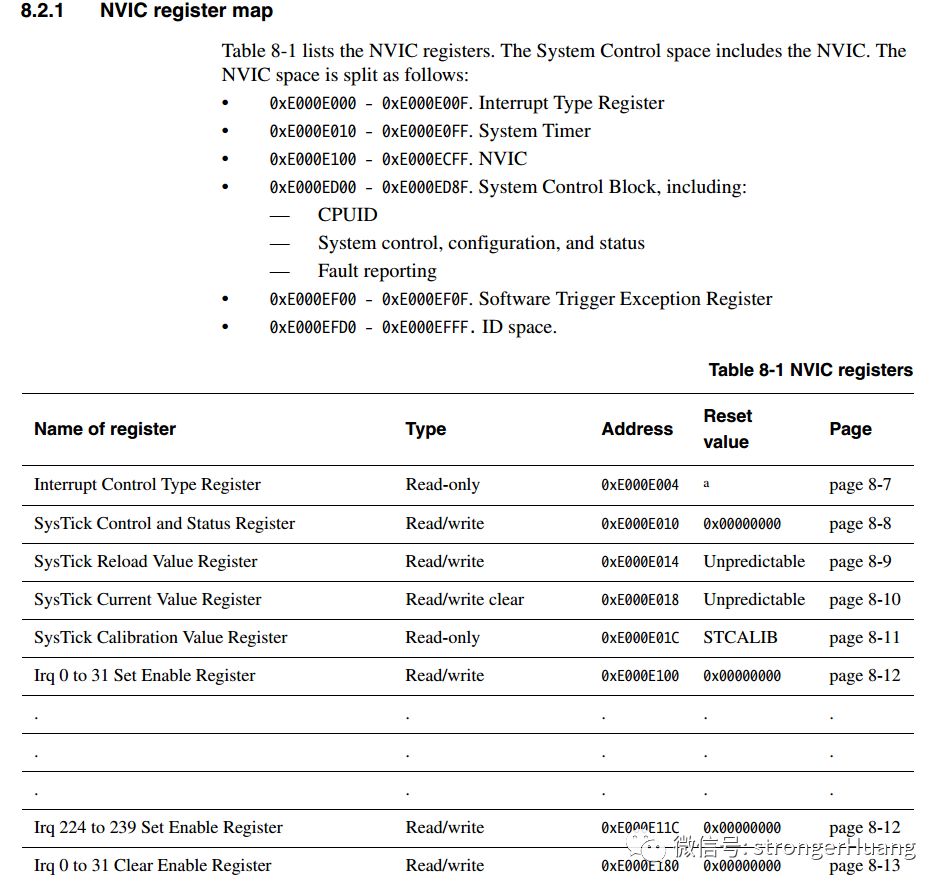

NVIC寄存器

NVIC寄存器,需查看對應的內核(Cortex-M)手冊,在ARM官網能找到(M3也有對應的中文翻譯版,大家可以自己網上搜索)。 內核中的寄存器和我們STM32參考手冊中寄存器一樣,不同的Bit位代表含義不同。 但是,對于NVIC來說,由于包含眾多優先級相關配置,寄存器數量相對較多(NVIC寄存器族)。 ?

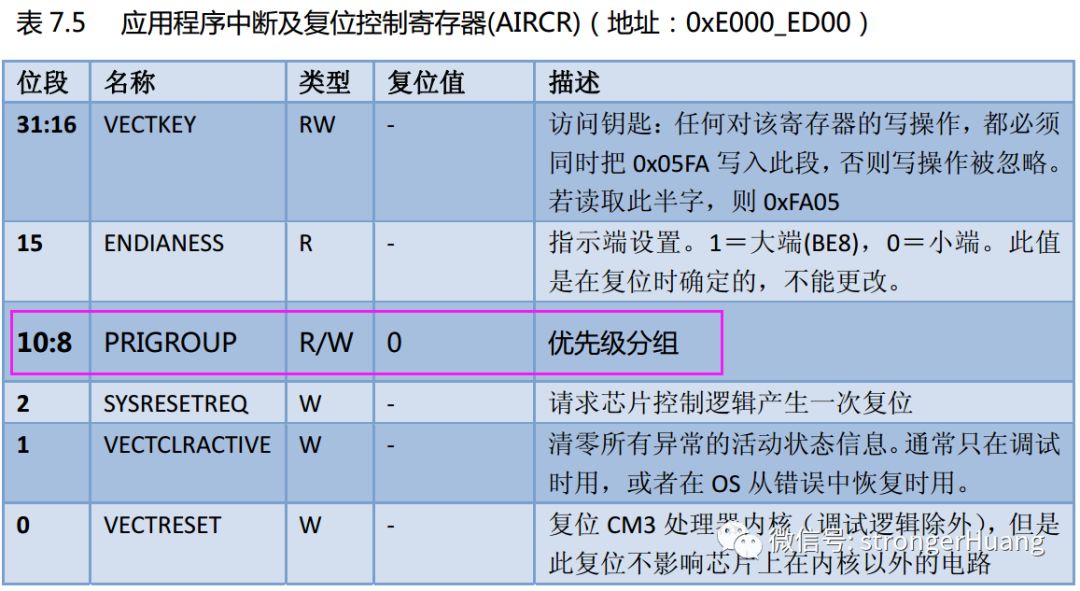

?拿M3來說,優先級分組的配置,位于NVIC的AIRCR應用程序中斷及復位控制寄存器中:

?

?拿M3來說,優先級分組的配置,位于NVIC的AIRCR應用程序中斷及復位控制寄存器中: ?這里推薦閱讀之前我寫過的一篇文章:Cortex-M中斷在RTOS中的應用及注意事項

?這里推薦閱讀之前我寫過的一篇文章:Cortex-M中斷在RTOS中的應用及注意事項

中斷入口

額外提下一個小伙伴問的問題:為什么外部中斷8和9都使用同一個中斷?void EXTI9_5_IRQHandler(void)

{

if(EXTI_GetITStatus(EXTI_Line8) != RESET)

{

/* 代碼 */

EXTI_ClearITPendingBit(EXTI_Line8);

}

if(EXTI_GetITStatus(EXTI_Line9) != RESET)

{

/* 代碼 */

EXTI_ClearITPendingBit(EXTI_Line9);

}

}

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

mcu

+關注

關注

146文章

17824瀏覽量

360129 -

控制器

+關注

關注

114文章

16959瀏覽量

182839 -

STM32

+關注

關注

2289文章

11011瀏覽量

362244

發布評論請先 登錄

相關推薦

熱點推薦

一天一個嵌入式面試知識(1:中斷處理機制詳解)

立即響應(優先級高)

需經過系統調度(優先級可控)

典型應用

外部事件響應(如UART數據到達)

系統服務調用(如文件讀寫)

三、中斷處理流程解析

以STM32為例,

發表于 03-21 10:18

使用CH32V103C8TC設置中斷優先級分組時,編譯報錯的原因?

使用CH32V103C8TC設置中斷優先級分組時,設置為NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);編譯報錯

而使用NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

卻不會報

發表于 09-27 06:03

CH32V103 使用中斷優先級分組0時報錯

使用CH32V103C8TC設置中斷優先級分組時,設置為NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);而使用NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);卻不會報錯

發表于 09-23 13:52

freertos中斷優先級在哪設置

FreeRTOS是一個流行的實時操作系統,它廣泛應用于嵌入式系統開發。在FreeRTOS中,中斷優先級是一個重要的概念,因為它決定了中斷處理的順序和響應時間。 1. 理解

通過I2C PWM IC控制伺服,可以為伺服控制進行高優先級中斷嗎?

() 大約需要 100 毫秒才能完成請求。

我怎樣才能避免那里的事情。

我可以為伺服控制進行高優先級中斷嗎?

使用 Arduino IDE。

發表于 07-12 06:20

請問有什么方法降低WIFI中斷的優先級?

因為項目對時序輸出要求比較嚴格,WIFI中斷優先級比硬件定時器中斷優先級要高,在定時器中斷里面對GPIO管腳控制被延長執行,請問有什么方法降

發表于 06-19 07:37

評論