這篇文章來源于DevicePlus.com英語網(wǎng)站的翻譯稿。

引言

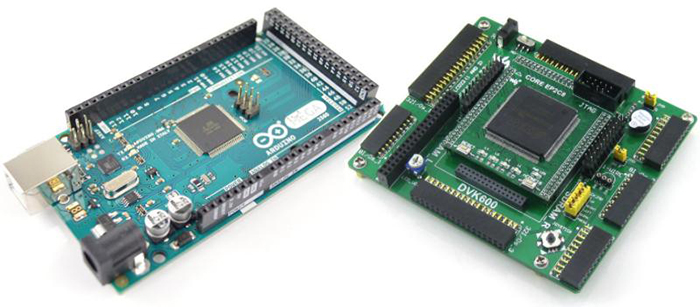

迄今為止,我們的嵌入式系統(tǒng)教程和項目已經(jīng)使用了多塊微控制器開發(fā)板,比如不同型號的Arduino微控制器板。使用微控制器時,用戶將微控制器上的數(shù)字和模擬接口引腳連至受控外圍電子設(shè)備,然后,用戶上傳包含一系列指令的軟件,微控制器會循環(huán)執(zhí)行這些指令。運行時,微控制器的核心處理器按照微控制器模塊的時鐘速率讀取并執(zhí)行這些指令。因此,我們可以看到,在某一時刻,微控制器通常只運行一條指令。

對于許多嵌入式系統(tǒng)項目來說,尤其是那些在入門微控制器模塊(比如Arduino開發(fā)板)上實現(xiàn)的項目,這種單獨的指令執(zhí)行并不影響性能。這是因為時鐘速度足夠快,以至于人類感官無法區(qū)分后續(xù)運行。然而,許多大型應(yīng)用可能需要不同的操作并行運行,這就使得微控制器實現(xiàn)變得非常復(fù)雜或完全不可能。現(xiàn)場可編程門陣列(簡稱FPGA)是一種不同的計算平臺,由于其固有的不同功能方式,能夠?qū)崿F(xiàn)微控制器無法實現(xiàn)的功能。

圖1:一塊Arduino微控制器開發(fā)板(左)和一塊Altera FPGA開發(fā)板(右)/ ?RobotShop & ?Waveshare

FPGA和微控制器的主要區(qū)別在于配置方法。用戶不需要像處理微控制器那樣上載一系列指令讓板載芯片解釋執(zhí)行,而是直接配置FPGA的硬件。這意味著用戶為FPGA編寫的程序不是重復(fù)執(zhí)行的一系列指令,而是如何配置內(nèi)部硬件以執(zhí)行不同任務(wù)的規(guī)劃。硬件以內(nèi)部邏輯門和存儲單元的形式出現(xiàn),最基本的級別就是多晶體管電路組合。

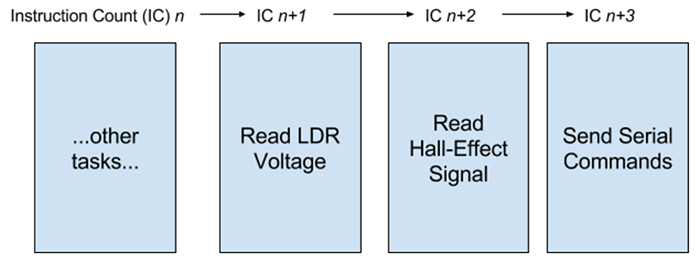

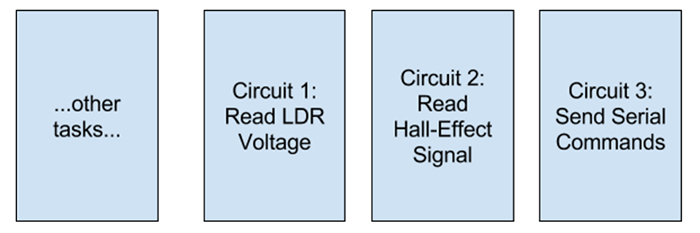

由于FPGA的項目實現(xiàn)實際上只是硬件連接,所以FPGA可以并行運行多個操作!想象一下,如果系統(tǒng)任務(wù)如下:讀取光敏電阻上的壓降;讀取霍爾效應(yīng)傳感器的輸入;并通過UART連接與另一個設(shè)備進(jìn)行通信。微控制器方案的程序流程圖可能如下所示:

請注意不同任務(wù)是串行完成的。而FPGA則可以使用不同電路分別執(zhí)行三個任務(wù),因此允許系統(tǒng)并行執(zhí)行所有三個操作。因此,F(xiàn)PGA方案的項目實現(xiàn)原理將如下所示:

上述例子只是很簡單地解釋了微控制器方案與運行和FPGA方案與運行之間的區(qū)別,這一點很重要。實際上,F(xiàn)PGA的內(nèi)部項目實現(xiàn)取決于項目本身,微控制器可能通過并行化執(zhí)行指令來提高性能。關(guān)鍵的一點是這兩種架構(gòu)實現(xiàn)相同任務(wù)的方式不同:微控制器串行執(zhí)行指令,而FPGA則通過路由內(nèi)部硬件實現(xiàn)功能行為。

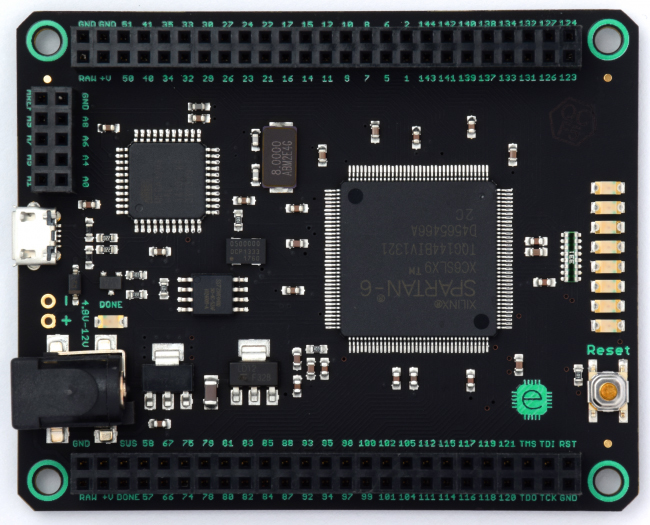

許多FPGA開發(fā)板都可以當(dāng)作入門模塊使用,比如Digilent和Xilinx出售的Arty和Basys開發(fā)板。在本教程中,我們將使用Embedded Micro的Mojo V3。這是一款低成本板卡,也可用作入門模塊。我個人比較喜歡Mojo開發(fā)板,比如Basys 3,因為它帶有大量可與外部電路連接的插頭引腳!此外,Embedded Micro還提供許多很棒的教程,幫助開發(fā)人員使用FPGA(請參考附錄中的鏈接)!

圖2:Mojo V3開發(fā)板/ ?Embedded Micro

在本教程中,我們從一個基本的輸入/輸出示例開始,向您介紹Mojo開發(fā)板的編程過程。在第2部分中,我們會為您準(zhǔn)備一個更復(fù)雜的項目:硬件PWM實現(xiàn)!

本教程演示了如何使用Verilog硬件描述語言(稍后我們將詳細(xì)討論該語言)來配置Mojo!Verilog及其變體已經(jīng)成為行業(yè)常用軟件,所以您通過 Mojo項目學(xué)到的知識也能應(yīng)用到其他更高級的開發(fā)板上!

所需軟硬件如下:

硬件:

Mojo V3開發(fā)板

Micro USB電纜

Windows或Linux電腦(不幸的是,目前不支持Mac操作系統(tǒng))

紅色LED

1 x 150?或類似電阻(用于LED限流)

2 x 10k?電阻(用于按鈕下拉)

面包板和跳線

軟件:

Mojo Loader(將設(shè)計實現(xiàn)上傳至FPGA)

ISE Design Suite(編寫和綜合Verilog代碼的IDE)

在下載頁面上向下滾動,直到看到標(biāo)有“ISE Design Suite”的部分

Mojo 基本項目(所有項目都將以Mojo提供的該項目骨架為基礎(chǔ))

比如說,我們想只有當(dāng)兩個外部按鈕都按下時,才能點亮一個外部LED。首先,我們注意到這是一個數(shù)字系統(tǒng),因為按鈕輸入電壓和LED輸出電壓只能取兩個值中的一個:0伏或3.3伏。我們可以用邏輯0表示0伏,用邏輯1表示3.3伏,從而對輸入端和輸出端的所有可能電壓值進(jìn)行二進(jìn)制編碼。實際上,1和0是“高”和“低”數(shù)字電壓信號的另一種表達(dá)方式。

下表總結(jié)了按鈕輸入的所有值和對應(yīng)的LED輸出值:

| 輸入1(按鈕1) | 輸入2(按鈕2) | 輸出(LED) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

熟悉布爾代數(shù)(研究二進(jìn)制值和二進(jìn)制值的不同運算)的人會把這個雙輸入單輸出系統(tǒng)看作與(AND )門。與門的工作原理是只有當(dāng)兩個輸入都是1時輸出才是1,這正是我們想要的按鈕和LED配置!許多邏輯門將輸出值定義為輸入值的函數(shù)。要查看所有邏輯門的信息,請點擊附件中的鏈接!

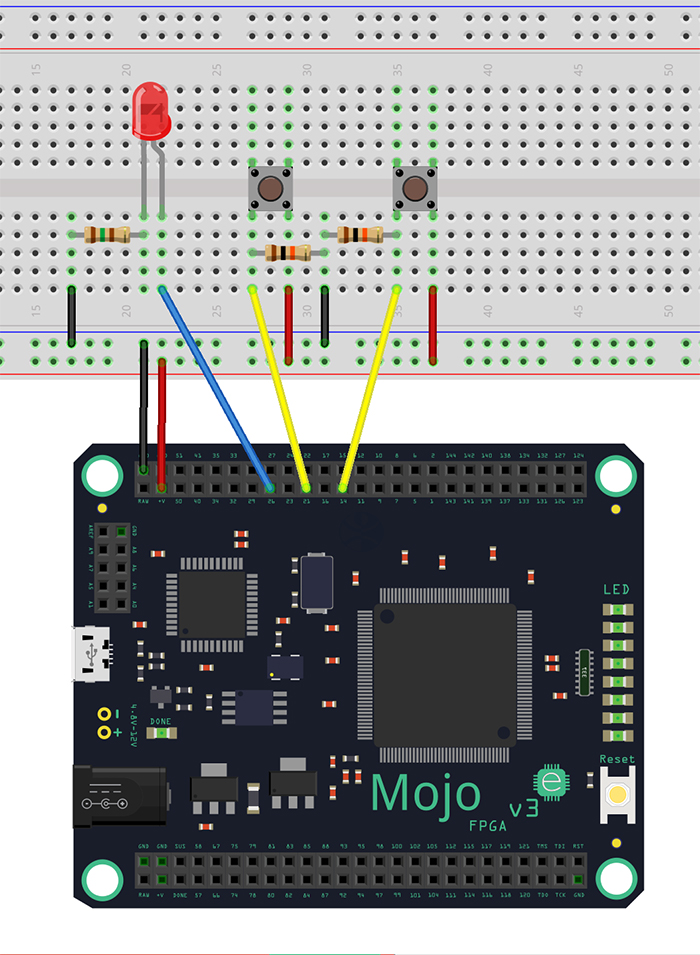

我們首先按下圖所示將按鈕和LED連至Mojo開發(fā)板:

圖3:Mojo開 發(fā)板連接一個LED和兩個按鈕的接線圖(通過Fritzing創(chuàng)建;Mojo Fritzing文件由Michael Earls制作)

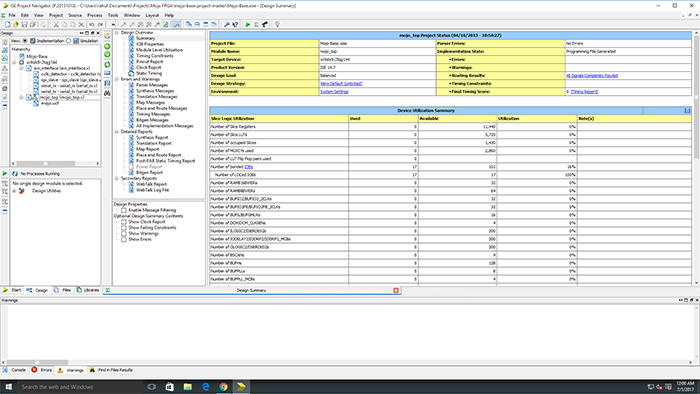

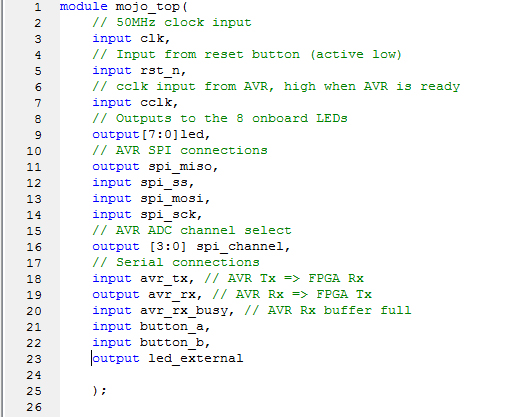

我們現(xiàn)在可以對Mojo進(jìn)行編程。啟動ISE并打開您下載的基礎(chǔ)項目。屏幕應(yīng)該如下所示:

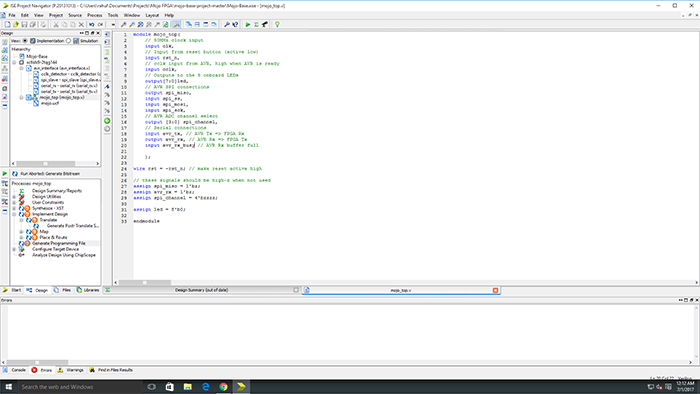

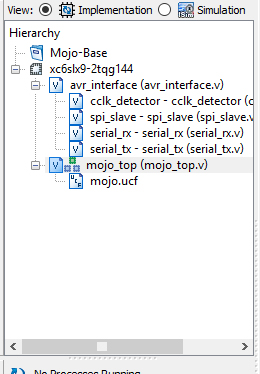

在窗口左側(cè),您應(yīng)該看到一個含有不同文件的層次結(jié)構(gòu)。雙擊文件mojo_top.v。該文件中的Verilog代碼應(yīng)該在屏幕右側(cè)彈出。

現(xiàn)在,我們簡單介紹一下Verilog語言及其文件結(jié)構(gòu)。首先需要注意的是,Verilog不是傳統(tǒng)意義上的編程語言。如前所述,F(xiàn)PGA的內(nèi)部硬件是可配置的。而Verilog語言則是設(shè)計人員和FPGA實現(xiàn)軟件(本文為ISE Design Suite)之間的接口。更具體地說,實現(xiàn)軟件讀取Verilog代碼并通過內(nèi)部算法將其轉(zhuǎn)換成一系列邏輯門,從而實現(xiàn)代碼指定的功能。因此,Verilog被稱為硬件描述語言,簡稱HDL。

Verilog代碼分為相互作用的多個不同模塊——這些模塊類似于其他編程語言的函數(shù)。這些模塊可以有多個輸入和輸出,模塊內(nèi)部的代碼會指定如何根據(jù)不同的輸入值驅(qū)動輸出。您可能會注意到,不同模塊可以分布在多個Verilog .v文件中。Mojo基礎(chǔ)項目包含幾個.v文件:AVR、SPI和串行功能。mojo_top.v文件是中心Verilog模塊,該模塊指定FPGA的主要行為。ISE足夠智能,能識別這是程序的中心(“主”)模塊。在屏幕左側(cè)的文件層次結(jié)構(gòu)中,您會看到mojo_top.v文件位于列表頂部。

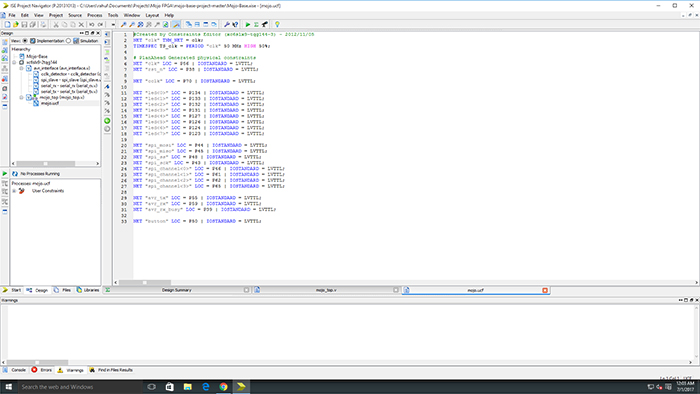

除Verilog .v文件外,您還會看到一個擴(kuò)展名為.ucf的文件,該文件代表用戶約束文件(User Constraints File)。在這個文件中,用戶在他或她的項目中為輸入和輸出(I / O)連接指定名稱,并確定與這些信號相關(guān)的引腳和I/O標(biāo)準(zhǔn)。我們開始編輯這個文件。在左側(cè)瀏覽器中雙擊文件名,該文件會在右側(cè)的新選項卡中打開。

您會看到這個文件中已經(jīng)存在幾條指令。這些指令指定了板上連接的名稱,比如板載LED和不同通信總線的連接。向下滾動至文件末尾,按鍵盤上的“Enter”鍵創(chuàng)建一個新行。我們要添加三條指令,分別對應(yīng)兩個按鈕輸入引腳和一個LED輸出引腳。 我們要做的就是按照文件中其他指令的格式編寫新指令即可!

您可以復(fù)制文件中以“NET”開頭的任何一條指令,然后在文件底部粘貼三次,修改行首引號內(nèi)的字符串以及“P”后面的數(shù)字。在本教程中,我們將使用14和21腳作為按鈕輸入,26腳作為LED輸出,因此我們應(yīng)在文件底部添加以下指令:

NET “button_a” LOC = P14 | IOSTANDARD = LVTTL;

NET “button_b” LOC = P21 | IOSTANDARD = LVTTL;

NET “l(fā)ed_external” LOC = P26 | IOSTANDARD = LVTTL;

請確保您選擇的引腳不與UCF文件指定的引腳沖突。

現(xiàn)在您的UCF文件應(yīng)該是這樣的:

現(xiàn)在我們已經(jīng)指定項目的具體信號名稱及其關(guān)聯(lián)連接,我們可以編寫代碼,將LED輸出描述為按鈕輸入信號的函數(shù)。您可能已經(jīng)猜到了,這需要修改mojo_top模塊。

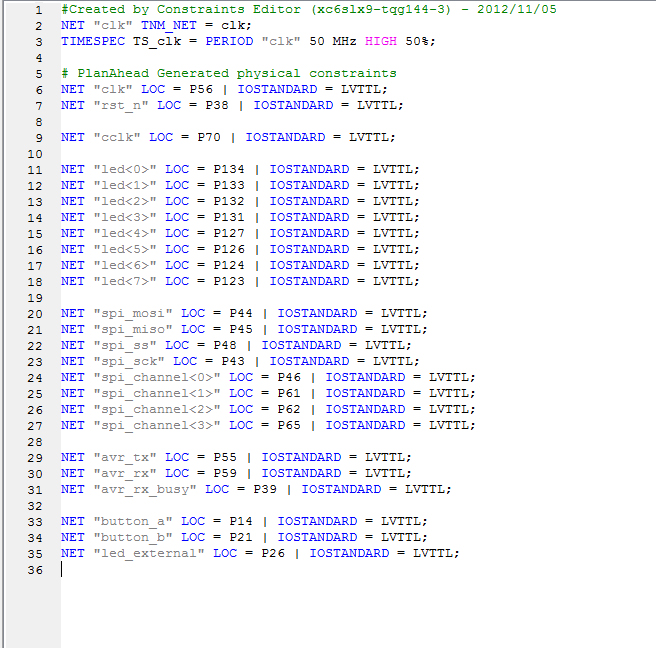

模塊聲明部分的頂部是單詞“module”(模塊),然后是模塊名稱(本例中模塊名稱為mojo_top)以及模塊將要使用的輸入和輸出信號列表。我們需要將兩個按鈕信號名稱和LED信號名稱添加到該連接列表中,使得信號能夠成為輸入和輸出。要做到這一點,我們可以在信號列表末尾添加以下程序:

input button_a,

input button_b,

output led_external

現(xiàn)在,模塊頭應(yīng)該是這樣的:

至此,我們已經(jīng)為按鈕和外部LED聲明了信號名稱,并為這些信號分配了Mojo開發(fā)板I/O引腳,并且在Verilog中指定這些信號分別是輸入和輸出。現(xiàn)在,我們所要做的就是定義LED點亮的條件!更具體地說,我們需要指定發(fā)光二極管開啟(二進(jìn)制1)和關(guān)閉(二進(jìn)制0)的情況。

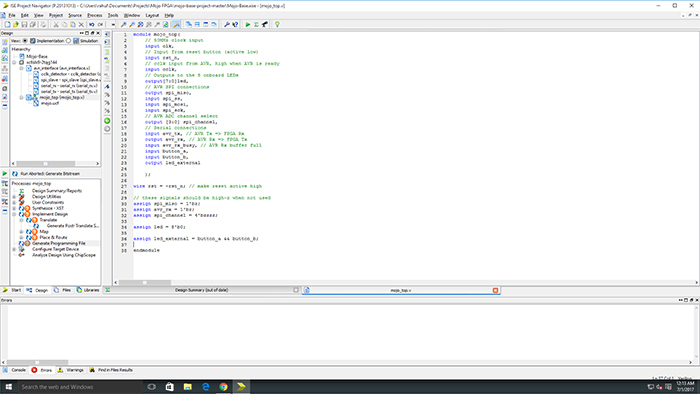

回想之前的討論,我提到LED的操作行為與布爾與(AND)函數(shù)完全相同。在Verilog中,我們用符號&&表示布爾與(AND)運算。我們想要將按鈕輸入的與函數(shù)結(jié)果分配給LED。實現(xiàn)此功能的Verilog代碼如下:

assign led_external = button_a && button_b;

將這行指令添加到模塊末尾就可以實現(xiàn)我們所需的行為。打開基礎(chǔ)項目時,我們會看到這行程序上方本來就存在許多程序行,這些程序設(shè)置了其他不同信號,比如板上SPI和板載LED信號,在本項目中我們不會使用這些信號。

現(xiàn)在,完整模塊應(yīng)該是這樣的:

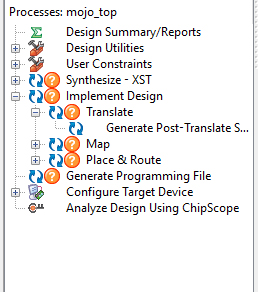

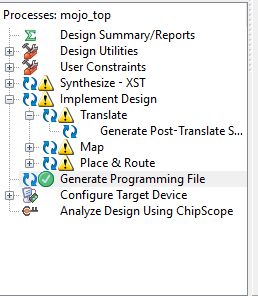

要對FPGA進(jìn)行編程以實現(xiàn)我們指定的行為,我們必須生成一個編程文件,其格式為.bin文件。發(fā)出命令之后,ISE會綜合我們的設(shè)計(檢查錯誤并運行測試),然后實現(xiàn)設(shè)計(定義實現(xiàn)指定行為所需的內(nèi)部門結(jié)構(gòu)),并生成這個編程文件。要運行此過程,請雙擊左下窗口中的“Generate Programming File”(生成編程文件)按鈕。

在編程文件生成的過程中,ISE會發(fā)出幾條丟失網(wǎng)絡(luò)和/或未路由網(wǎng)絡(luò)的警告。這些警告對于此實現(xiàn)并不重要,不會影響我們對FPGA的編程。我們沒有使用UCF中指定的所有信號,所以ISE才會發(fā)出這些警告。

編程文件生成完成后,ISE會在我們剛才雙擊的按鈕旁邊添加一個綠色對號。

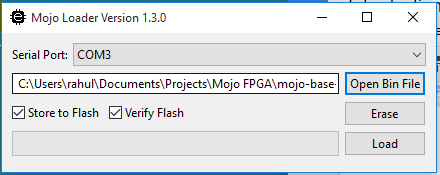

現(xiàn)在,我們所要做的就是將編程文件上傳到Mojo開發(fā)板上。首先,請確保按上圖所示將按鈕和LED連至Mojo的引腳。

其次,打開Mojo Loader軟件并選擇與Mojo相對應(yīng)的USB端口。然后,選擇ISE生成的.bin文件。您必須導(dǎo)航至項目目錄下的/syn/文件夾。在Mojo Loader內(nèi)打開.bin文件后,請點擊窗口右下方的“Load”(加載)按鈕。編程文件就開始向Mojo開發(fā)板上傳。

該過程完成后,您就可以測試您的設(shè)計了!只有按下兩個按鈕時,LED燈才會點亮。恭喜,您已經(jīng)完成了您的第一個FPGA項目!我們還為您準(zhǔn)備了一個更復(fù)雜的硬件PWM項目,敬請查看本教程的第2部分!

審核編輯:湯梓紅

-

微控制器

+關(guān)注

關(guān)注

48文章

7923瀏覽量

153808 -

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614642 -

Embedded

+關(guān)注

關(guān)注

0文章

50瀏覽量

22705 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

5565瀏覽量

102762 -

Arduino

+關(guān)注

關(guān)注

189文章

6493瀏覽量

190218

發(fā)布評論請先 登錄

Altium推出智能FPGA開發(fā)板NanoBoard 300

Altium發(fā)布NanoBoard 3000 FPGA開發(fā)板

基于Xilinx FPGA的開發(fā)板及代碼

fpga開發(fā)板哪個好?fpga開發(fā)板推薦

FPGA開發(fā)板使用和配置方式

經(jīng)驗分享:如何選購FPGA開發(fā)板

關(guān)于FPGA開發(fā)板和原型驗證系統(tǒng)對比介紹

上位機(jī)和FPGA開發(fā)板--串口通信實驗

評論