亞穩態是我們在設計經常遇到的問題。這個錯誤我在很多設計中都看到過。有人可能覺得不以為然,其實你現在沒有遇到問題只能說明:

1. 你的發貨量還沒到一定的量級。

2. 你很幸運。

當問題一旦發生的時候,亞穩態的問題是非常難以定量的分析的,甚至復現也是非常困難的。為了不讓這樣的“玄學”問題困擾我們,我們在設計調試的時候,首先要把這類問題規避,才有助于我們撥開迷霧,找到問題的原因。設計的檢視也非常重要,不能說功能測試通過了,小批量發貨沒有問題產品就沒有潛在的隱患。

亞穩態與設計可靠性

設計數字電路時大家都知道同步是非常重要的,特別當要輸入一個信號到一個同步電路中,但是該信號由另一個時鐘驅動時,這是要在接口處采取一些措施,使輸入的異步信號同步化,否則電路將無法正常工作,因為輸入端很可能出現亞穩態(Metastability),導致采樣錯誤。這里我們對亞穩態的起因、危害、對可靠性的影響和消除仿真做一些介紹。

1.亞穩態發生的原因

在同步系統中,如果觸發器的setup time / hold time不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態,在這段時間里Q端毛刺、振蕩、固定的某一電壓值,而不是等于數據輸入端D的值。這段之間成為決斷時間(resolution time)。經過resolution time之后Q端將穩定到0或1上,但是究竟是0還是1,這是隨機的,與輸入沒有必然的關系。

2.亞穩態的危害

由于輸出在穩定下來之前可能是毛刺、振蕩、固定的某一電壓值,因此亞穩態除了導致邏輯誤判之外,輸出0~1之間的中間電壓值還會使下一級產生亞穩態(即導致亞穩態的傳播)。

邏輯誤判有可能通過電路的特殊設計減輕危害(如異步FIFO中Gray碼計數器的作用),而亞穩態的傳播則擴大了故障面,難以處理。

3.亞穩態的解決辦法

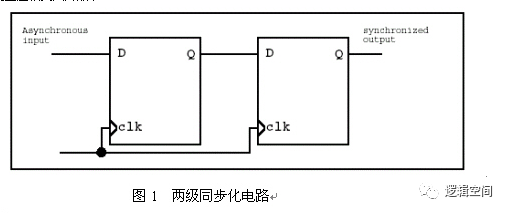

只要系統中有異步元件,亞穩態就是無法避免的,因此設計的電路首先要減少亞穩態導致錯誤的發生,其次要使系統對產生的錯誤不敏感。前者要靠同步來實現,而后者根據不同的設計應用有不同的處理辦法。用同步來減少亞穩態發生機會的典型電路如圖1所示。

在圖1中,左邊為異步輸入端,經過兩級觸發器同步,在右邊的輸出將是同步的,而且該輸出基本不存在亞穩態。其原理是即使第一個觸發器的輸出端存在亞穩態,經過一個CLK周期后,第二個觸發器D端的電平仍未穩定的概率非常小,因此第二個觸發器Q端基本不會產生亞穩態。注意,這里說的是“基本”,也就是無法“根除”,那么如果第二個觸發器Q出現了亞穩態會有什么后果呢?后果的嚴重程度是由你的設計決定的,如果系統對產生的錯誤不敏感,那么系統可能正常工作,或者經過短暫的異常之后可以恢復正常工作,例如設計異步FIFO時使用格雷碼計數器當讀寫地址的指針就是處于這方面的考慮。如果設計上沒有考慮如何降低系統對亞穩態的敏感程度,那么一旦出現亞穩態,系統可能就崩潰了。

4.亞穩態與系統可靠性

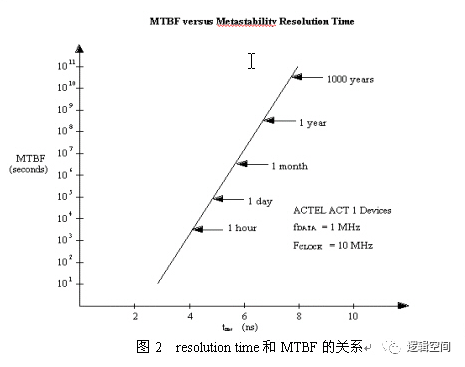

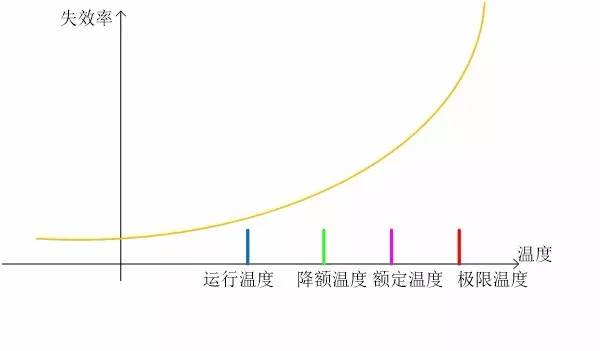

使用同步電路以后,亞穩態仍然有發生的可能,與此相連的是MTBF(Mean Time Between Failure),亞穩態的發生概率與時鐘頻率無關,但是MTBF與時鐘有密切關系。有文章提供了一個例子,某一系統在20MHz時鐘下工作時,MTBF約為50年,但是時鐘頻率提高到40MHz時,MTBF只有1分鐘!可見降低時鐘頻率可以大大減小亞穩態導致系統錯誤的出現,其原因在于,提供較長的resolution time可減小亞穩態傳遞到下一級的機會,提高系統的MTBF,如圖2所示。

5.總結

亞穩態與設計可靠性有非常密切的關系,當前對很多設計來說,實現需要的功能并不困難,難的是提高系統的穩定性、可靠性,較小亞穩態發生的概率,并降低系統對亞穩態錯誤的敏感程度可以提高系統的可靠性。

審核編輯:湯梓紅

-

數字電路

+關注

關注

193文章

1638瀏覽量

81730 -

亞穩態

+關注

關注

0文章

47瀏覽量

13498 -

可靠性

+關注

關注

4文章

269瀏覽量

27102

原文標題:亞穩態的傳播

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

利用IDDR簡化亞穩態方案

FPGA同步復位和異步復位的可靠性特點及優缺點

xilinx資料:利用IDDR簡化亞穩態

FPGA觸發器的亞穩態認識

亞穩態問題解析

在FPGA復位電路中產生亞穩態的原因

亞穩態與設計可靠性

評論