- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

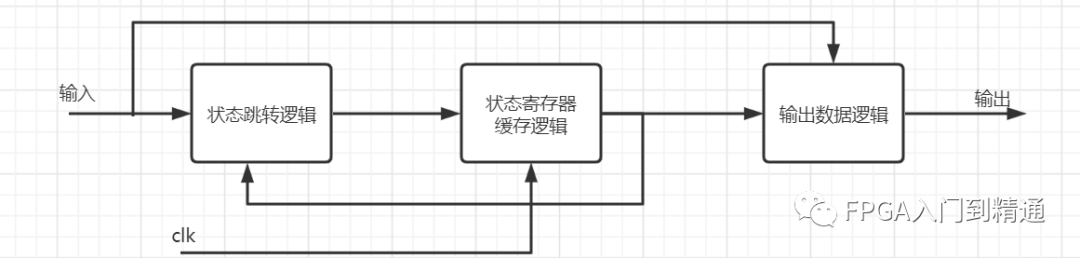

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動(dòng)作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

-

寄存器

+關(guān)注

關(guān)注

31文章

5434瀏覽量

124572 -

信號

+關(guān)注

關(guān)注

11文章

2853瀏覽量

78308 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

493瀏覽量

28258

發(fā)布評論請先 登錄

FPGA工程師:如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)?

FPGA狀態(tài)機(jī)為什么會跑飛

華清遠(yuǎn)見FPGA代碼-狀態(tài)機(jī)

簡述使用QII狀態(tài)機(jī)向?qū)绾蝿?chuàng)建一個(gè)狀態(tài)機(jī)

FPGA之狀態(tài)機(jī)的功能簡述

基于FPGA實(shí)現(xiàn)狀態(tài)機(jī)的設(shè)計(jì)

FPGA之狀態(tài)機(jī)練習(xí):設(shè)計(jì)思路(5)

FPGA之狀態(tài)機(jī)練習(xí):設(shè)計(jì)思路(4)

FPGA:狀態(tài)機(jī)簡述

詳細(xì)介紹FPGA狀態(tài)機(jī)的設(shè)計(jì)和應(yīng)用

如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

基于FPGA的狀態(tài)機(jī)設(shè)計(jì)

評論